|           | 432-2 |

|-----------|-------|

| Document# |       |

THE MICROPROCESSOR CONTROLLED DATA AND TIMING GENERATOR

MODEL RS-432, MODEL RSM-432

USER'S GUIDE

INTERFACE TECHNOLOGY

Document Control #432-UG-001

Copyright 1976

Revised: 24 May 1976

16 August 1976 30 April 1980

## MODEL RS-432, RSM-432 DOCUMENTATION

This sheet is prepared on a per serial number basis. It describes your specific model number, serial number and configuration. It identifies which drawings are applicable from the drawing package supplied in this manual. It also identifies the applicable options. It is recommended that this page not be removed from this manual and shall be kept by the customer for future reference in cases of service, applications assistance, etc.

| Your Model                             | Number is: Model                                        |

|----------------------------------------|---------------------------------------------------------|

| Your Serial                            | Number is: Serial #                                     |

|                                        |                                                         |

| Applicable                             | sections of this manual are appropriately marked below: |

|                                        | Basic RS-432 User's Guide                               |

|                                        | RSM-432 Users Guide Supplement                          |

|                                        | 16 Bit Parallel Interface User's Guide                  |

|                                        | IEEE 488-1978 Interface User's Guide                    |

|                                        | RS-232/TTY Interface User's Guide                       |

|                                        | 8 Bit Parallel Interface User's Guide                   |

|                                        | Card Reader with Interface User's Guide                 |

| ************************************** | RS-232/C, TTY Interface Drawings/Schematics             |

|                                        | Dual 8 Bit Parallel 16 Bit Parallel Interface           |

|                                        | Top Assembly RS-432, RS-432E (Dwg# 10011287)            |

|                                        | Al, Top Logic Panel, Standard (Dwg# 10011062)           |

| ·                                      | Al, Top Logic Panel, RSM (Dwg# 10011062-001)            |

|                                        | A2, Bottom Logic Panel, Standard (Dwg# 10011061)        |

|                                        | A2, Bottom Logic Panel, RSM (Dwg# 10011061-001)         |

|                                        | A3, Front Panel (Dwg# 10011016)                         |

|                                        | A4, Rear Bottom Logic Panel (Dwg# 10011095)             |

|                                        | 256 Word/Program Memory Card (Dwg# 10011035)            |

|                                        | 1024 Word Memory Card (Dwg# 10011049)                   |

| na je <del>zama</del>                  | 256/1024 ROM Card (Dwg# 10011007)                       |

|                                        | Output Register Card (Dwg# 10011014)                    |

|                                        | 2K x 16 Word Memory Card (Dwg# 10011334)                |

|                                         | ALU Card (Dwg# 10011044)                                                 |                   |

|-----------------------------------------|--------------------------------------------------------------------------|-------------------|

|                                         | Timing Simulator Card (Dwg# 1001104.                                     | 3)                |

| *************************************** | Input Comparator Card (Dwg# 1001104                                      | 7)                |

|                                         | Card Reader Interface Card (Dwg# 100 (Also 8 Bit Parallel Interface Card |                   |

|                                         | IEEE 488-1978 Interface Card #1 (Dw                                      | g# 10011013)      |

|                                         | IEEE 488-1978 Interface Card #2 (Dw                                      | g# 10011012)      |

|                                         | RS-232/TTY Interface Card (Dwg# 100                                      | 11066)            |

|                                         | RS-232/TTY DC Converter (Dwg# 10011                                      | 336)              |

|                                         | Power Supply, Transformer Schematics                                     | s (Dwg# 2835)     |

|                                         | Power Supply, Transformer Schematics                                     | s (Dwg# 6015-S01) |

|                                         |                                                                          |                   |

|                                         |                                                                          |                   |

|                                         |                                                                          |                   |

| PREPARED BY                             | • ************************************                                   | DATE:             |

## TABLE OF CONTENTS

| Section | Title                                 | Page |

|---------|---------------------------------------|------|

| I.      | INTRODUCTION                          | 1    |

| 1.1     | General Description                   | ī    |

| 1.2     | Physical Description                  | 2    |

| 1.3     | Specifications                        | 2    |

| II.     | INSTALLATION                          | 6    |

| 2.1     | Mechanical                            | 6    |

| 2.2     | Electrical                            | 6    |

| 2.3     | Initial Checkout                      | 7    |

| 2.4     | Calibration                           | 8    |

| III.    | OPERATION                             | 9    |

| 3.1     | Controls and Indicators               | 9    |

| 3.1.1   | Front Panel Loading                   | 11   |

| 3.1.1.1 | Program Memory Loading Procedure      | 11   |

| 3.1.1.2 | Word Memory Loading                   | 12   |

| 3.2     | Inputs and Outputs                    | 13   |

| 3.2.1   | Output Control Signals                | 14   |

| 3.2.2   | Input Control Signals                 | 14   |

| 3.2.3   | Output Clocks                         | 14   |

| 3.2.3.1 | Free-Running Clocks                   | 15   |

| 3.2.3.2 | Gated Clocks                          | 15   |

| 3.2.3.3 | Sync Signal                           | 16   |

| 3.2.4   | Input Clock                           | 17   |

| 3.2.5   | Output Data                           | 18   |

| 3.2.6   | Input Data                            | 18   |

| 3.2.7   | Output Timing Relationship            | 18   |

| 3.2.8   | Logic Ground                          | 19   |

| 3.3     | Operating Procedure and Example       | 19   |

| 3.3.1   | Operating Procedure                   | 19   |

| 3.3.2   | RS-432 Example                        | 20   |

| 3.3.2.1 | Problem                               | 20   |

| 3.3.2.2 | I/O Signals                           | 20   |

| 3.3.2.3 | Program Coding Sheet, Program Loading |      |

|         | and Execution                         | 21   |

| IV.     | CIRCUIT DESCRIPTION AND PROGRAMMING   | 25   |

| 4.1     | Microprocessor Description            | 25   |

| 4.1.1   | Operation/Program Considerations      | 26   |

| 4.2     | Word Generator                        | 38   |

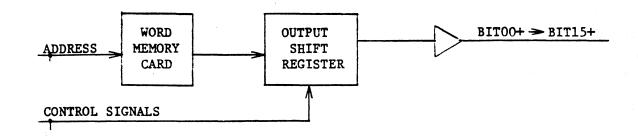

| 4.2.1   | Word Memory                           | 38   |

| 4.2.2   | Address Control                       | 38   |

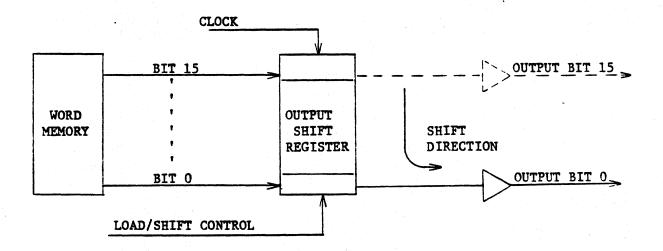

| 4.2.3   | Output Shift Register                 | 40   |

| 4.2.4   | Period Counter and Output Clocks      | 41   |

| 4.3     | Options                               | 41   |

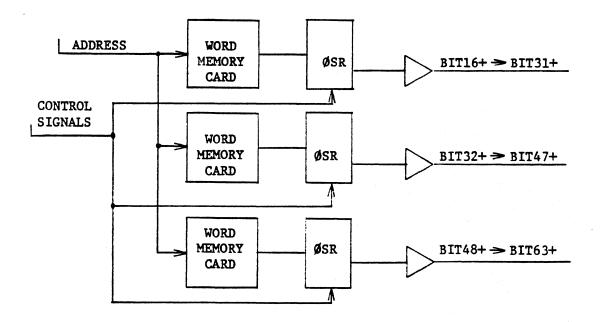

| 4.3.1   | Additional Output Register Cards      | 41   |

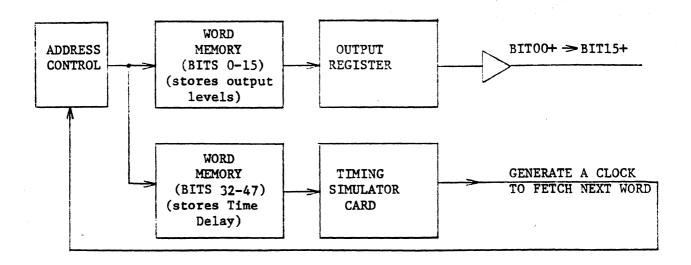

| 4.3.2   | Timing Simulator Option               | 44   |

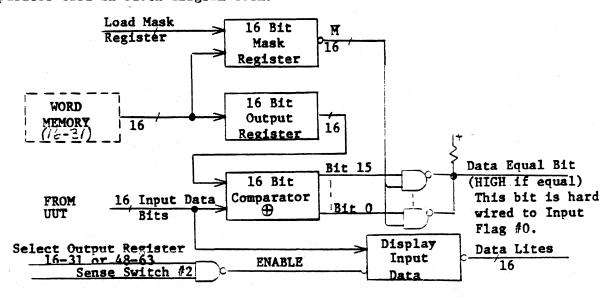

| 4.3.3   | Input Comparator Option               | 46   |

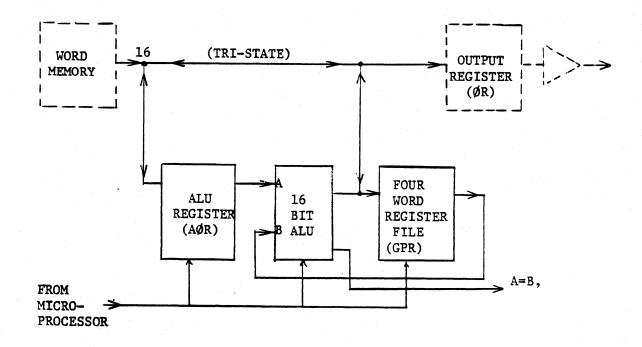

| 4.3.4   | ALU Output Register Card              | 48   |

| 4.4     | Program Examples                      | 53   |

## TABLE OF CONTENTS

## APPENDECIES

| Section    | Title                                          | Page |

|------------|------------------------------------------------|------|

| Appendix A | Condensed Instruction Set                      | A1   |

| Appendix B | Input/Output Connector                         | В1   |

| Appendix C | RS-432 Output Connector                        | C1   |

| Appendix D | RS-432 Output Connector                        | D1   |

| Appendix E | RS-432 Programming Sheet (Coding)              | E1   |

| Appendix F | RS-432 Word Memory Programming Sheet           | F1   |

| Appendix G | RS-432 PROM Card                               | G1   |

| Appendix H | RS-432 Input Compare                           | Н1   |

| Appendix I | RSM Supplemental User's Guide                  | 11   |

| Appendix J | 16 Bit Parallel Interface User's Guide         | J1   |

| Appendix K | IEEE 488-1978 Interface User's Guide           | K1   |

| Appendix L | RS-232-C/TTY Interface                         | L1   |

| Appendix M | 8 Bit Parallel Interface User's Guide          | M1   |

| Appendix N | Card Readers User's Guide                      | N1   |

| Appendix O | Dual 8 Bit Parallel/16 Bit Parallel Interface. | 01   |

| Appendix P | Schematics Drawings                            | P1   |

| Appendix Q | List of Representatives                        | Q1   |

|            |                                                |      |

# LIST OF FIGURES

| Figure | Title                                                                  | <u>Page</u> |

|--------|------------------------------------------------------------------------|-------------|

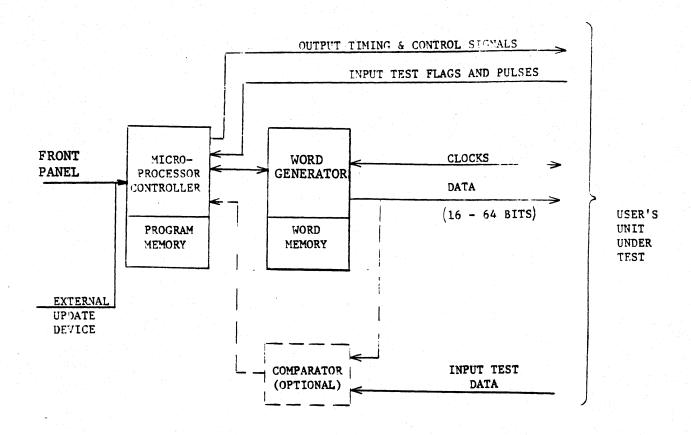

| 1      | RS-432 Block Diagram                                                   | 2           |

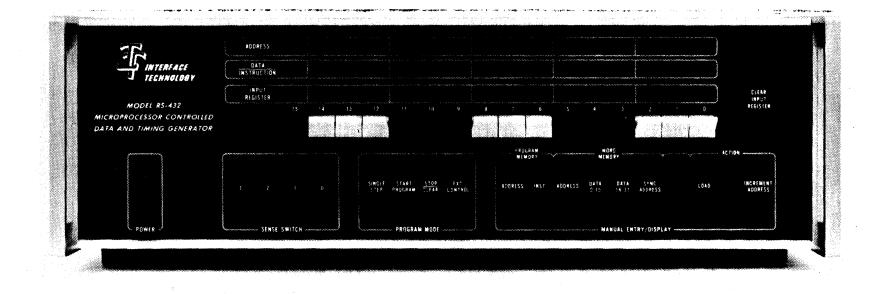

| 2      | RS-432 Microprocessor Controlled Data and Timing Generator Front Panel | 3           |

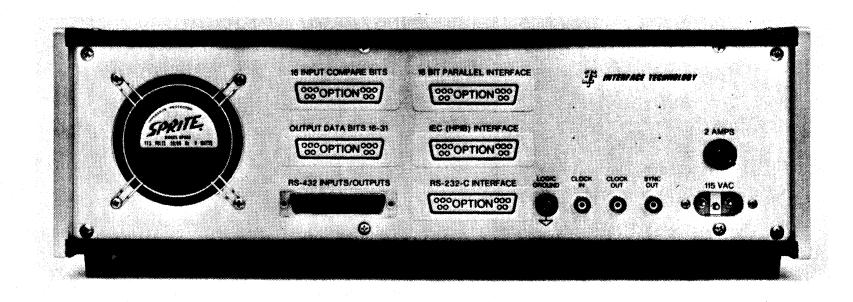

| 3      | RS-432 Microprocessor Controlled Data and Timing Generator Back Panel  | 4           |

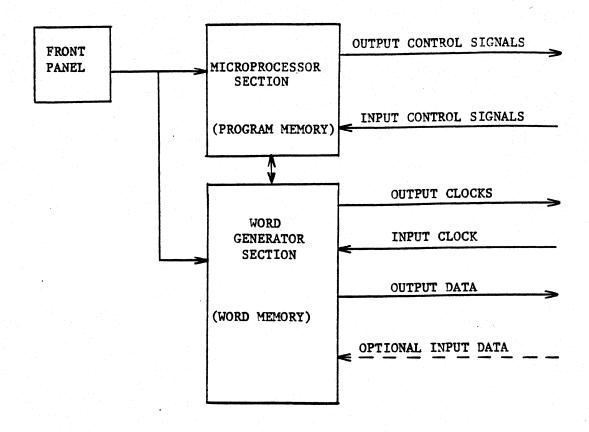

| 4      | Simplified I/O Block Diagram                                           | 14          |

| 5      | Free-Running Clocks                                                    | 15          |

| 6      | Output Clocks and Data Relationship                                    | 16          |

| 7      | Input Clock Relationship                                               | 17          |

| 8      | Input Clock/Data Out Timing Relationship                               | 17          |

| 9      | Clock/Data Timing Relationship                                         | 18          |

| 10     | Data Timing Relationship                                               | 19          |

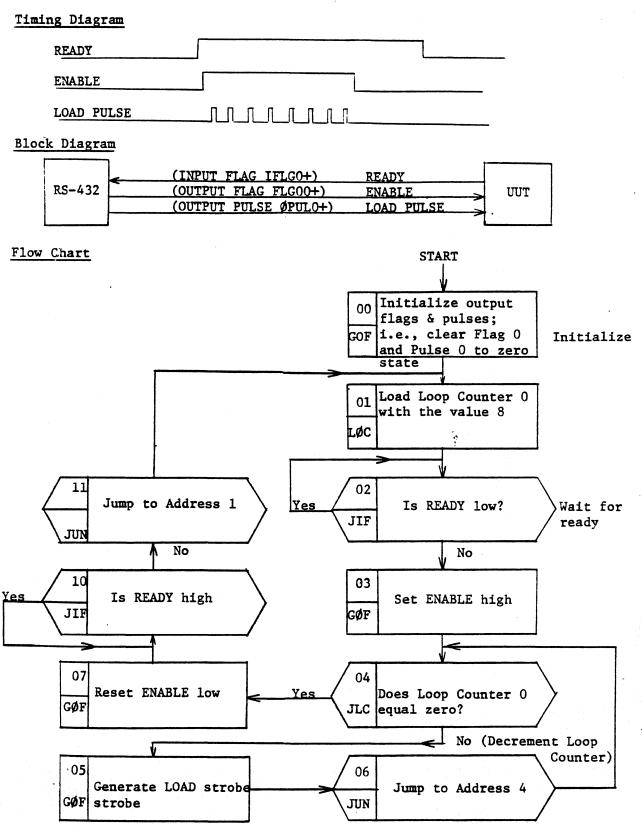

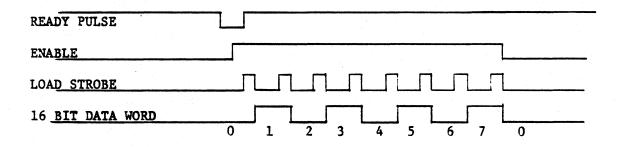

| 11     | RS-432 I/O Signal Diagram for Example                                  | 21          |

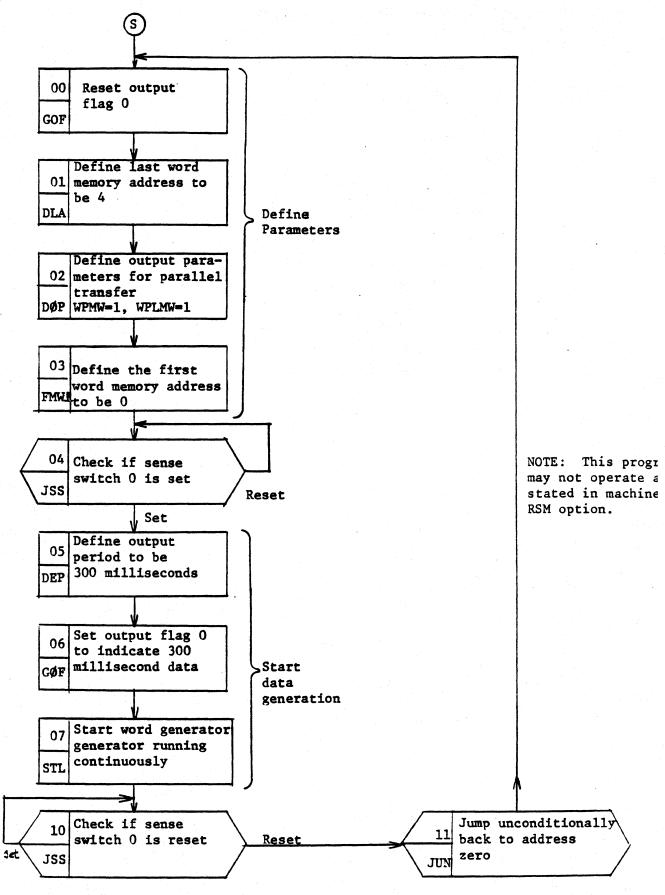

| 12     | RS-432 Flow Chart for Example                                          | 22          |

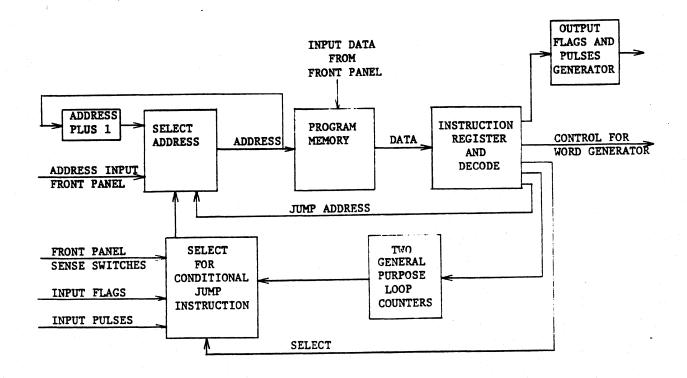

| 13     | Microprocessor Section Block Diagram                                   | 25          |

| 14     | Word Generator Architecture                                            | 39          |

| 15     | Output Shift Register                                                  | 40          |

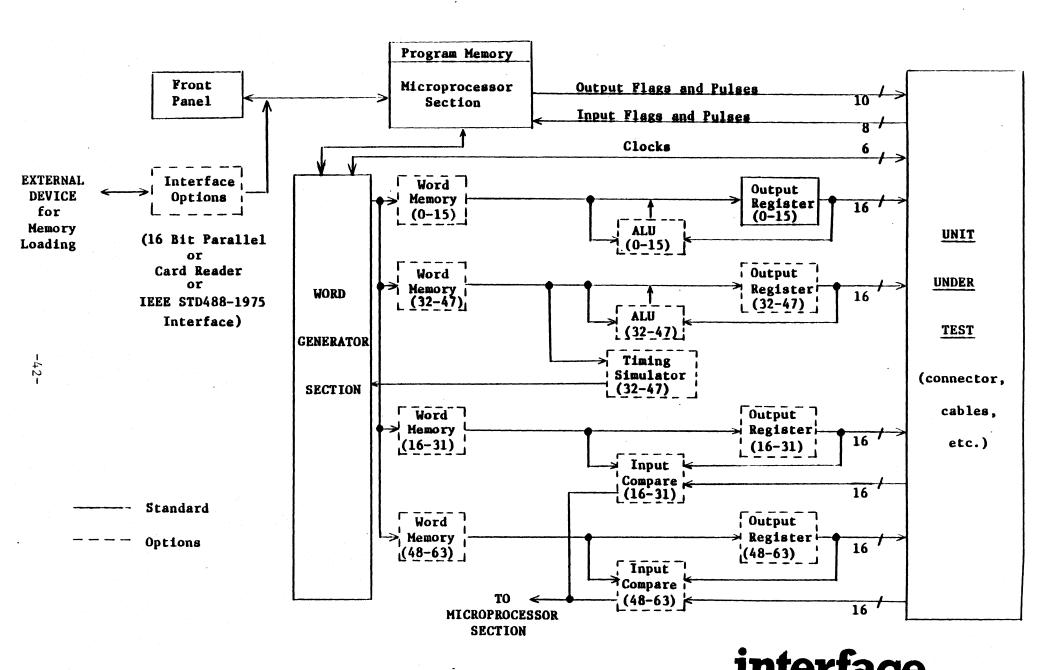

| 16     | RS-432 Block Diagram with Options                                      | 42          |

| 17     | One Output Register                                                    | 43          |

| 18     | Additional Output Registers                                            | 43          |

| 19     | Timing Simulator Block Diagram                                         | 45          |

| 20     | Input Comparator Block Diagram                                         | 46          |

| 21     | ALU Option Block Diagram                                               | 48          |

| 22     | Program Timing                                                         | 62          |

## LIST OF TABLES

| <u>Table</u> | Title                                                              | Page |

|--------------|--------------------------------------------------------------------|------|

| 1            | RS-432 General Specifications                                      | 5    |

| 2            | Initial Checkout Procedure                                         | 7    |

| 3            | Manual Entry/Display Switches                                      | 10   |

| 4            | RS-432 Programming Sheet (Coding)                                  | 23   |

| 5            | RS-432 Word Memory Programming Sheet                               | 24   |

| 6            | Instruction Set                                                    | 28   |

| 7            | Front Panel Switch Configuration for Greater than 32 Bit Operation | 44   |

| 8            | ALU Functions                                                      | 51   |

#### PROPRIETARY NOTICE

This document and the technical data contained herein are proprietary to Interface Technology and shall not, without the written permission of Interface Technology, be used in any form or part to solicit competitive quotations from within customer complex or other competitive sources. The information provided herein may be used for operation and maintenance purposes or for purposes of incorporation into technical specifications and other documents which specify procurement from Interface Technology.

#### WARRANTY

Interface Technology warrants each instrument manufactured to be free of defects in material and workmanship for a period of one year from the date of shipment to the original purchaser. Interface Technology will service, replace, or adjust any defective part or parts, free of charge, when the instrument is returned to Interface Technology freight prepaid, and when examination reveals that the fault has not occurred because of misuse or abnormal conditions of operation. Instruments repaired beyond the effective date of warranty or when abnormal useage has occurred will be charged at applicable rates. Interface Technology will submit an estimate for such charges commencing repair if so requested. For any questions concerning this warranty or shipping, call Interface Technology or our Sales Representative in your area.

#### PERSONNEL SAFETY

The equipment described in this manual contains voltages hazardous to human life and safety and which is capable of inflicting personal injury.

For all procedures involving component insertion or withdrawal, the equipment must be powered off to prevent component damage. It is also recommended for such procedures that the primary power cord be disconnected from the equipment's rear panel connector to prevent accidental contact with primary power circuits.

While physical measures have been built into the equipment to prevent accidental contact with high voltages during maintenance and troubleshooting procedures, the user should still exercise caution. Careless probing inside the equipment may result in the exposure of high voltage terminals.

Before operating the unit ensure that the primary power outlet includes a functional protective ground (earth) circuit. Do not defeat the unit's internal protective ground circuit to chassis by using a two conductor adapter plug or other such device.

## I. INTRODUCTION

The RS-432 Microprocessor Controlled Data & Timing Generator provides the user with a self-contained instrument that can be programmed to generate special-purpose digital test signals. It is a highly flexible digital test system, enabling the user to custom-program all his required test data, as well as required timing, control, and handshake signals.

The User's Guide describes the RS-432 entirely from an operational stand point. It provides programming procedures and specific applications and describes the various options that can be added to the basic RS-432. Organizationally, the Guide starts with a general introduction of the RS-432 from a block diagram stand point. It then proceeds to the descriptions of the various major sections of the RS-432 and provides examples of various programs.

#### 1.1 GENERAL DESCRIPTION

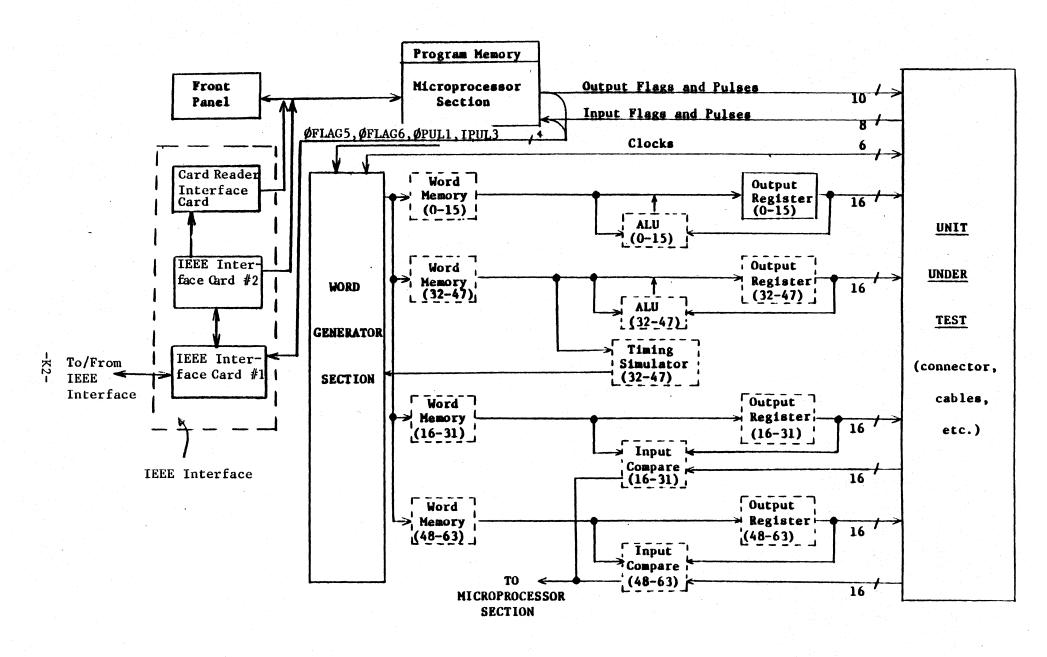

The RS-432 integrates two digital concepts into a single machine. First, it incorporates a high-speed programmable microprocessor that the user programs to generate all his required timing, control, and handshake signals. The microprocessor also provides the overall decision-making and control of the test system. Second, it uses an internal high-speed word generator to store the user's required test data. The word generator receives operating parameters and commands from the microprocessor in such a way that the two sections work together to generate the required test data and control signals.

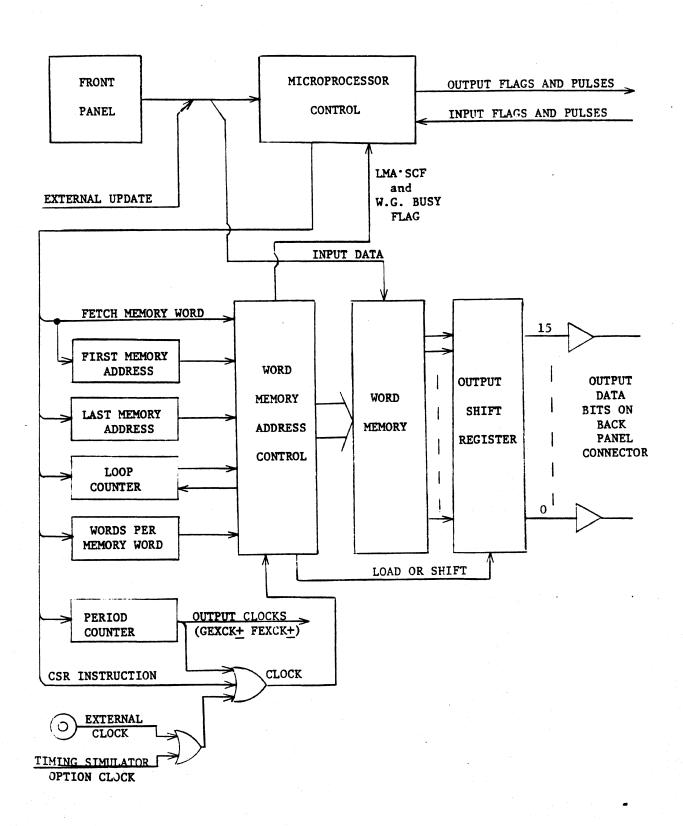

Figure 1 illustrates the RS-432 architecture. Data is input into the microprocessor program memory and word generator memory from either the front panel or an external device (card, tape reader, etc.). Once the program and word memories are loaded and the machine is started (START PROGRAM switch on front panel is activated), the microprocessor begins executing instructions. These instructions, in turn, generate the required test signals.

The user cannot directly control the word generator from the front panel; the word generator must receive commands from the microprocessor to generate the test data. A program must be written and executed in the microprocessor to generate the required word generator control.

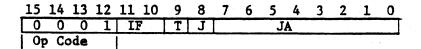

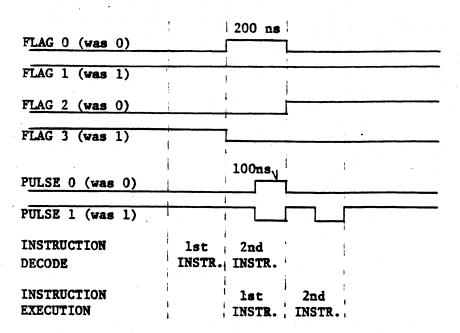

The microprocessor section is the heart of the RS-432. It controls/monitors output and input flags and pulses to and from the user's unit under test (UUT). It executes 16 basic instructions at a rate of 200 nanoseconds per instruction.

The word generator section contains a clock generator that develops the basic output frequency or word rate. It also contains additional logic that controls the output shift registers and generates the various clocks output by the RS-432. The RS-432 can generate as many as 64 parallel bits.

Several options are available to expand the RS-432 capability. The ALU option provides for output pattern generation capability. The timing simulator option allows nonperiodic output rates. The input comparator option provides the RS-432 with the capability of testing input data against data prestored in word memory.

Figure 1 RS-432 BLOCK DIAGRAM

#### 1.2 PHYSICAL DESCRIPTION

The RS-432 is packaged in a metal enclosure. The front panel contains control and data switches to allow manual communication with the internal logic of the RS-432. The back panel houses the input/output connectors and BNC jacks that allow the physical interconnect between the RS-432 and the UUT. Figures 2 and 3 are photographs of the front and back panels respectively.

#### 1.3 SPECIFICATIONS

Table 1 summarizes the general specifications of the RS-432.

Figure 2. RS-432 MICROPROCESSOR CONTROLLED DATA AND TIMING GENERATOR FRONT PANEL

Figure 3. RS-432 MICROPROCESSOR CONTROLLED DATA AND TIMING GENERATOR BACK PANEL

#### Table 1. RS-432 GENERAL SPECIFICATIONS

#### MEMORY SIZE:

Program Memory: 64 or 256 words; each word (instruction) is a 16-bit parallel word.

Word (Generator) Memory: Word memory may range from 64 to 4K words, and word size may range from 16 to 64 bits. Refer to the Word Generator Section (Page 37) for a table of allowable configurations.

#### MEMORY SPEED:

Program Memory: Instruction execution speed is 5 MHz (200 nsec per instruction).

Word (Generator) Memory: Maximum data access time is 10 MHz (100 nsec per word).

#### **OUTPUT SIGNALS:**

All output signals are SN74128N 50-ohm TTL line drivers. Each output is capable of driving 30 TTL gates. Each output signal drives a twisted pair wire and is accessible on the back panel connector or BNC connector. Typical rise times (assuming 50-ohm terminated line) for each driver is 3 nsec. Drive characteristics of the SN74128N are presented in Texas Instrument's Data Book.

#### INPUT SIGNALS:

All input signals are one TTL input load. Each input is a twisted pair wire, accessible on the back panel connector. Input signal low and high limits are -0.5 and +5.5 volts, respectively.

#### POWER:

115 VAC @ 60 Hz  $(\pm 10\%)$ . Typical dissipation is 80 watts. The AC is fused at 2 amp.

#### DIMENSIONS AND WEIGHT:

Height: 5.25 inches

Depth: 13.00 inches (extended 22 inches)

Width: 17.00 inches (rack mountable)

Weight: 24 pounds (extended 34 pounds)

## OPERATING TEMPERATURE:

Operating temperature range is  $0^{\circ}$  to  $65^{\circ}$ C. The RS-432 is cooled by means of a fan mounted on the rear panel.

#### II. INSTALLATION

Installation of the RS-432 consists simply of rack mounting, if required, and mating to the proper input/output signal connectors.

#### 2.1 MECHANICAL

The RS-432 is shipped ready for use as a stand-alone benchtop signal generator. The folding stand option, if ordered, is mounted and ready for use on the bottom side of the RS-432.

Rack-mounting kit material, if ordered, is packaged with the RS-432. Installation of the rack mounting hardware requires removal of the RS-432 side plates to expose the appropriate holes to which the rack-mount ears can be attached. Slide hardware can also be attached to the side plates if desired.

The RS-432 weighs approximately 24 pounds, with its center of gravity to the left and rear of the enclosure's geometrical center. Appropriate measures should be taken to assure proper mounting within the equipment rack.

#### 2.2 ELECTRICAL

The RS-432 is shipped ready for operation. The enclosed AC cord should be plugged into the 115 VAC 60 Hz receptacle located on the RS-432 back panel. A two-amp 115 VAC fuse is preinstalled in the fuse holder located on the back panel.

All RS-432 input/output signal interconnections are made via the back panel. These I/O signals can be categorized in three groups: (1) those considered to be the standard RS-432 I/O signals, (2) those that are options to the standard RS-432, and (3) those concerned with external loading and control of the RS-432.

Group 1 signals are accessible, via the back panel, through a 78-pin Cannon-type connector and three BNC-type connectors. The 78-pin connector contains all the standard RS-432 input and output signals that are under program control. These signals and their pin assignments are listed in the Appendix. Typically, these signals will be cabled to the user's UUT with a special cable built by the user for his application.

The BNC connectors contain signals that interface with the word generator clock section of the RS-432 - - SYNC OUT, CLOCK OUT, and CLOCK IN. Briefly, SYNC OUT occurs each time the word generator address counter accesses a user defined address (refer to Page 16 for detailed explanation); CLOCK OUT and CLOCK IN are equivalent to GESCK- and GINCK-, respectively, found on the 78-pin connector discussed previously.

Group 2 signals are options to the standard RS-432, and are also available via the back panel through appropriately marked connectors. Signals in this group include additional parallel data outputs and input data compare bits. These signals and their pin assignments are also found in the Appendix.

Group 3 signals are also optional and would be provided for either a 16-bit parallel interface, an RS-232C connector compatible interface (for RS-232C or TTY current loops), an IEEE 488-1975 standard (HPIB) compatible

interface, or a mark/sense hand-feed card reader interface. Appropriate connector locations are marked on the RS-432 back panel. Refer to the Appendix for a detailed listing of pin assignments.

#### 2.3 INITIAL CHECKOUT

The following is a short initial checkout procedure that can be performed when the RS-432 is first received.

First, with power off, manually exercise all front panel paddle switches (except the POWER ON switch) to verify that they are operational. Note that some switches are alternate action, whereas others are momentary action.

Next, perform all the steps listed in Table 2. Detailed descriptions of all front panel controls and indicators appear in Section 3.1.

This procedure is a quick check "go/no go" of the RS-432. It verifies that the RS-432 is operational from the standpoint of front panel loading, including the application of AC power, DC power supply, and internal control logic. It does not verify the instruciton execution or I/O data generation capability.

Table 2. INITIAL CHECKOUT PROCEDURE

|         | Table 2. INITIAL CHEC                                                                               | CKOUT PROCEDURE                                                                          |

|---------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| STEP    | ACTION                                                                                              | VERIFY                                                                                   |

| l<br>la | Turn POWER ON switch on<br>Put all sense switches to                                                | LED above POWER switch should be lit.                                                    |

| 2       | Depress STOP/CLEAR switch                                                                           | LED above START PROGRAM and EXT CONTROL should go OFF.                                   |

| 3       | Depress PROGRAM MEMORY ADDRESS switch                                                               | LED above switch should be lit. ADDRESS, DATA/INSTRUCTION LED may have several LEDs lit. |

| 4       | Depress CLEAR INPUT REGISTER switch                                                                 | INPUT REGISTER LEDs should be all zero.                                                  |

| 5       | Depress data toggle switches<br>O thru 6                                                            | INPUT REGISTER LEDs should be lit in bit positions 0 thru 6.                             |

| 6       | Depress LOAD switch                                                                                 | ADDRESS LEDs should be lit in bit positions positions 0 thru 6 only.                     |

| 7       | Depress PROGRAM MEMORY DATA switch                                                                  | LED above switch should be lit.                                                          |

| 8       | Depress LOAD switch                                                                                 | DATA LEDs should be lit in bit positions 0 thru 6 only.                                  |

| 9       | Depress INCREMENT switch                                                                            | ADDRESS LED 7 should be lit, all others should be zero; DATA LEDs may change.            |

| 10      | Repeat steps 3 thru 9 but replace switch with the DATA MEMORY ADDR the PROGRAM MEMORY DATA switch w | ESS switch, and replace                                                                  |

#### 2.4 CALIBRATION

Prior to shipment, the RS-432 has been calibrated and functionally tested. Since the RS-432 is a digital signal generator, calibration is limited to periodic (3 months) verification of the power supply voltage. Refer to the power supply and transformer schematics for location of the various controls referenced below. The necessary adjustments are as follows:

#### a. Voltage

Connect voltmeter to power supply connections on the lower logic panel. Adjust the power supply voltage to +5.000 +/- 0.050 Vdc.

## b. Current Limiting

Connect voltmeter to power supply connections on the lower logic panel. Rotate current limit potentiometer CCW until the output voltage decreases approximately 15 mVdc. Rotate the current limit potentiometer CW approximately 1/8 turn.

In order to troubleshoot the unit, the user should reference the maintenance drawing set which has been configured to each unit's option complement. Verification of the RS-432's fundamental functions may be accomplished by performing the operations of Sections 2.3 and 3.1 of the User's Guide. If the fault cannot be located and corrected, the unit should be returned to Interface Technology.

## III. OPERATION

#### 3.1 CONTROLS AND INDICATORS

This section describes the function of the front panel switches. Figure 2 shows the position of the switches on the front panel. It is suggested that the reader become familiar with the microprocessor and word generator before studying this section in detail.

POWER: This alternate-action power switch supplies 115 VAC to the 5-volt power supply.

Lower position = POWER OFF

Upper position = POWER ON (The LED above the switch will light, verifying power on).

INPUT REGISTER AND SWITCHES: The 16 input register momentary action switches labeled 0 thru 15 input data into the input register. Pressing a switch transfers a "1" into the respective register bit which, in turn, lights its associated LED. The 16-bit input register supplies manual input data for the RS-432.

CLEAR INPUT REGISTER: This momentary action switch clears all input register bits to the zero state.

MANUAL ENTRY/DISPLAY: These momentary action switches define which register or memory location is to be updated and/or displayed on the ADDRESS and DATA/INSTRUCTION LEDs. The six switches to the left select the destination register, and the two to the right define the action to be performed on the designated register. Depressing any of the six switches on the left lights the respective LED and turns off the remaining five (i.e., these switches are bailed). Table 3 indicates the data displayed on the ADDRESS and DATA/INSTRUCTION LEDs and the action that may take place for each of the six destination registers.

PROGRAM MODE: These four momentary action switches determine the program mode:

STOP/CLEAR: Pressing the STOP/CLEAR switch performs the following functions:

- #1. Stops program execution; START PROGRAM LED will go off.

- #2. Stops word generator from sequencing. Word generator can then be started only by executing a start word generator loop (STL) instruction.

- #3. Clears external control; EXT CONTROL LED will go off (if on); i.e., gives update control to the front panel.

- #4. Clears input pulse falgs.

START PROGRAM: Pressing the START PROGRAM switch starts program execution. The START PROGRAM LED lights, and program starts at the present address stored in the PMA register.

EXT CONTROL: Pressing the EXT CONTROL switch enables an external device (computer, card reader, etc) to load, update, and control the RS-432. The EXT CONTROL LED turns on. Programming from the front panel is inhibited, although the six register display LEDs can still be selected to display their respective data. Note that an external device can also request and gain control without the depressing of the EXT CONTROL switch. The EXT CONTROL led can only be exstinguished with STOP CLEAR switch.

SINGLE STEP: If both the START PROGRAM and EXT CONTROL LEDs are OFF, pressing the SINGLE STEP switch will execute one program instruction. By continual pressing, the generator can single-step through the entire program.

If one of the instructions executed during this Single Step process is an STL instruction, the word generator will receive one clock pulse for each activation of the SINGLE STEP switch. Simultaneously, the program will also execute one instruction for each activation of the SINGLE STEP switch. If the instruction sequence is a start word generator followed by a halt until the word generator is complete instruction, the operator could literally spend hours attempting to single step through the word generator if the generator required many clock pulses to complete its task. This effort can be bypassed by pressing the STOP/CLEAR switch, which will reset the Word Generator Busy flag. Continued pressing of the SINGLE STEP switch will then continue to Single Step through the program.

SENSE SWITCHES: These alternate-action switches enable on-line communication with the program. Each switch is debounced and synchronized with the program to eliminate erroneous inputs. The jump-on sense switch (JSS) instruction can then test each sense switch for the upper or lower position. Some sense switches are uses for display purposes as well as program control.

## 3.1.1. Front Panel Loading

The following description provides step-by-step procedures for loading both the program memory and word memory. Program Example 4 (page 58) is used as input data.

3.1.1.1. Program Memory Loading Procedure

#### Step Action

- 1 Press STOP/CLEAR switch.

- la Put all sense switches to lower position.

NOTE: Steps 2 thru 5 provide the "fetch" program memory address function.

- Press PROGRAM MEMORY ADDRESS switch. This selects the program memory address counter as the destination register.

- 3 Press CLEAR INPUT REGISTER switch.

- Input into the Input Register (press appropriate data switches for these bit positions which are to be a "l") the first program memory address location. For Program Example 4, all zeroes will be the input data (i.e., do not press any input register switches).

Press the LOAD switch. This action loads the Input Register data into the program memory address counter (i.e., program address 0 has been "fetched").

NOTE: Steps 6 thru 9 will load the first instruction into the program memory.

- Press the PROGRAM MEMORY INST (instruction) switch. This selects the program memory as the destination register. The particular program memory word that is the destination register is the one at the location defined by the program memory address counter being displayed on the ADDRESS lights (in this case, address 0).

- 7 Press the CLEAR INPUT REGISTER switch.

- Input into the input register the desired program instruction data for program address 0. For Program Example 4, this would be as shown below:

|   | 15 | 14 | 13 | 12 | 11   | 10   | 9 | 8. | 7 | 6   | 5  | 4  | 3 | 2 | 1 | 0      |  |

|---|----|----|----|----|------|------|---|----|---|-----|----|----|---|---|---|--------|--|

|   | 1  | 0  | 0  | 0  | 1    | 0    | 0 | 0  | 0 | 0   | 0  | 0  | 1 | 0 | 1 | 0      |  |

| - | DI | EΡ |    |    | 11 1 | ısec | - |    |   | Val | ue | 10 |   |   |   | $\Box$ |  |

9 Press the LOAD switch. The data in Step 8 will appear on the DATA/INSTRUCTION lights.

NOTE: Steps 10 thru 13 will load the second instruction into the program memory

- Press the INCREMENT ADDRESS switch. The program memory address counter will increment by 1, as can be verified by observing the ADDRESS lights.

- 11 Press the CLEAR INPUT REGISTER switch.

- 12 Input the next program instruction data into the input register.

- 13 Press the LOAD switch

NOTE: Step 14 will load the remaining memory locations.

Repeat Steps 10 thru 13 until all desired program memory locations are loaded. For this example, the last program memory location to be loaded is at program address 6 (00000110). Note that unused program memory locations need not be cleared out; i.e., they are "don't care" locations.

## 3.1.1.2 Word Memory Loading

#### Step Action

1 Press the STOP CLEAR switch.

NOTE: Steps 2 thru 5 provide the "fetch" word memory address function.

- Press the WORD MEMORY ADDRESS switch. This selects the word memory address counter as the destination register.

- 3 Press the CLEAR INPUT REGISTER switch.

- Input into the input register (press appropriate data switches for the bit positions that are to be a "1") the first word memory address location.

- 5 Press the LOAD switch. This function loads the input register data into the word memory address counter.

NOTE: Steps 6 thru 9 will load the first data word into the word memory.

- Press the WORD MEMORY DATA 0-15 switch, which selects the word memory data bits 0-15 as the destination register. However, since there may be 4K memory words, the particular word that is the destination register is the one at the location defined by the word memory address counter (which is now displayed on the ADDRESS lights).

- 7 Press the CLEAR INPUT REGISTER switch.

- 8 Input into the input register the desired word data for the first data word.

- 9 Press the LOAD switch. Input data will appear on the DATA/INSTRUCTION lights.

NOTE: Steps 10 thru 13 will load the second data word into the word memory.

- Press the INCREMENT ADDRESS switch. The word memory address counter will increment by 1, as can be verified by observing the ADDRESS lights.

- 11. Press the CLEAR INPUT REGISTER switch.

- 12 Input the next data word into the input register.

- 13 Press the LOAD switch.

NOTE: Step 14 will load the remaining program memory location.

14 Repeat Steps 10 thru 13 until all desired word memory locations are loaded.

#### 3.2 INPUTS AND OUTPUTS

This section describes the RS-432 signal inputs and signal outputs, exclusive of the memory load interfaces such as the 16-bit parallel interface, RS-232C compatible interface, etc. It describes, in general terms, how these various signals are controlled. For a detailed description and explanation of these signals, refer to Section IV.

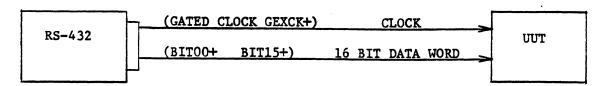

Figure 4 is a simplified diagram depicting the source and termination points for all inputs and outputs to be discussed in this section. All inputs present one TTL unit load to the UUT, whereas all outputs are driven from a 74128-type, 50-ohm line driver capable of driving 30 TTL unit loads.

Figure 4. SIMPLIFIED I/O BLOCK DIAGRAM

#### 3.2.1 Output Control Signals

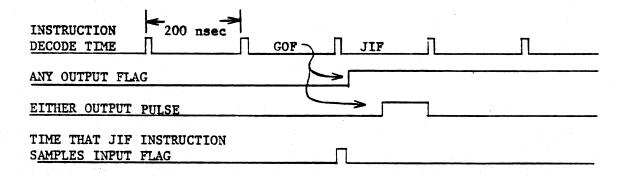

The microprocessor section directly controls two types of output control signals: eight output flags and two output pulses. The states of these ten lines are simultaneously controlled by a single microprocessor instruction. This instruction sets ("1") or resets ("0") the output flag lines, and can set, reset, pulse low, or pulse high the output pulse lines. Setting or resetting any flag or pulse line can occur as fast as 200 nanoseconds. All pulse lines have durations of 100 nanoseconds. Refer to Section 4 for detailed explanation of the generate output flags (GOF) instruction.

These output control signals are available on the standard 78 pin back panel connector. Pin assignments are indicated in the Appendix.

#### 3.2.2 Input Control Signals

The microprocessor section can directly sense two types of input control signals: four input flag lines and four input pulse lines. These input control signals are available on the standard 78-pin back panel connector. Refer to the Appendix for pin assignments. Quanitity may vary because some input control signals are used for options.

A microprocessor instruction can check the states of the four input flag lines for their set or reset conditions. External devices under test can use these lines to indicate a variety of conditions to the microprocessor section.

The input pulse lines feed latches internal to the microprocessor section. The microprocessor monitors latch outputs for pulse occurrence or absence. After interrogation, the microprocessor resets the particular latch that has been tested. Refer to Section 4 for a detailed explanation of the jump-on input flag (JIF) and jump-on input pulse (JIP) instructions.

#### 3.2.3 Output Clocks

Several clocks are available at the RS-432 back panel: the free-running clocks, gated clocks, and the sync signal. These clocks are generated by the word generator section.

#### 3.2.3.1 Free-Running Clocks

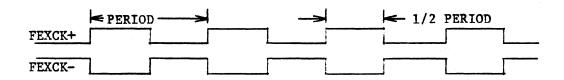

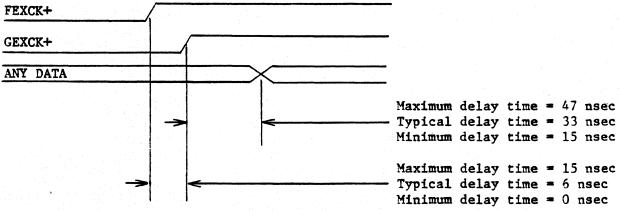

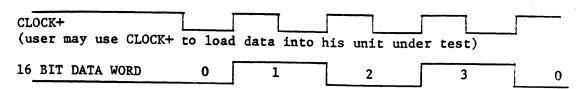

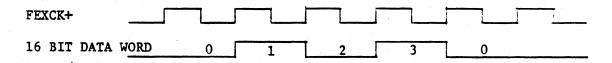

The user has access on the back panel 78-pin connector to both a free-running clock (FEXCK+) and an inverted free-running clock (FEXCK-) (Figure 5). Both clocks are square waves, with a frequency defined by the period counter in the word generator.

Figure 5. FREE-RUNNING CLOCKS

The plus sign on the signal mnemonic for the clock indicates that the output register will load new data or shift data when the FEXCK+ clock goes from low to high. The minus sign indicates that data will change when FEXCK- goes from high to low (refer to Figure 6).

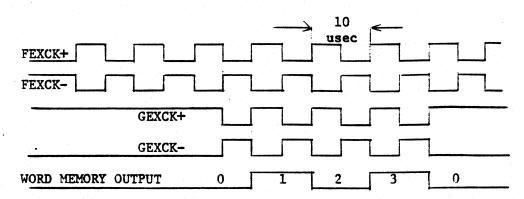

## 3.2.3.2 Gated Clocks

Two gated clocks (GEXCK+, GEXCK-) are also available on the back panel 78-pin output connector. These clocks are precisely synchronized with the free-running clocks, but they are gated on only when the word generator has been started by a start word generator loop (STL) instruction. They remain running until the word generator completes the transfer of the data block and the Word Generator Busy flag is reset. The gated clocks enable the user to transfer test data from the word generator into his system or UUT.

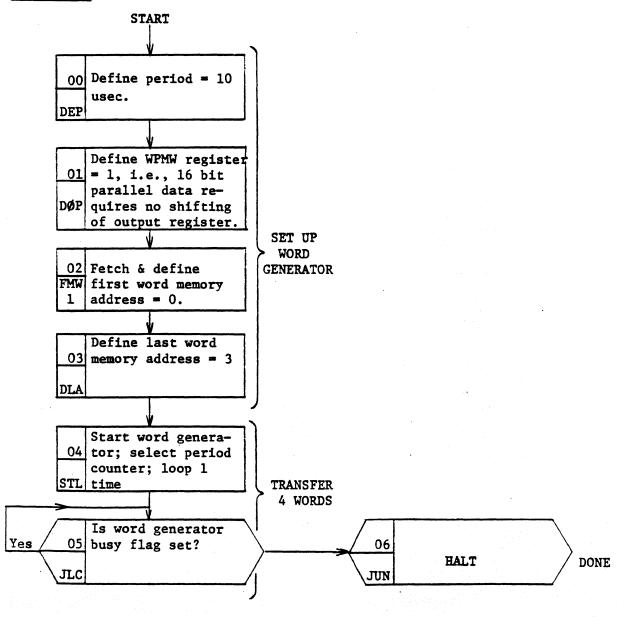

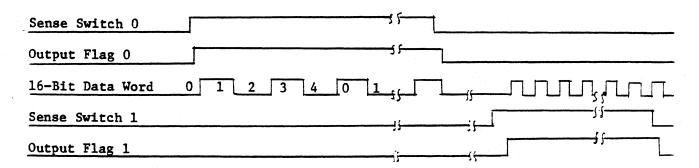

Figure 6 illustrates the relationship of the free-running clocks, gated clocks, and the word generator output data. The timing shown assumes the following:

- 1. First word memory address = 0

- 2. Last word memory address = 3

- 3. Parallel data transfer

- 4. Period counter = 10 microseconds

- 5. The word generator received an STL instruction that selects the period counter clock as the clock source and requests a loop count of 1.

Figure 6. OUTPUT CLOCKS AND DATA RELATIONSHIP

Again, note that the plus sign on the clock mnemonic indicates that the word data will change coincident with the low-to-high transition, whereas the minus sign indicates that the word data will change coincident with the high-to-low transition.

Note that the signal CLOCK OUT, which is available at a back panel BNC-type connector, is identical to the gated clock GEXCK- on the 78-pin I/O connector. However, it is rebuffered. Figure 6 shows the timing relationship.

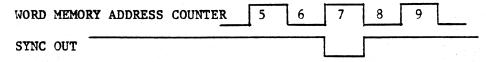

## 3.2.3.3 Sync Signal

The SYNC OUT signal available at a BNC-type connector on the back panel generates a sync pulse whenever the word memory address counter equals the word memory sync address register. This register can be loaded by activating the front panel WORD MEMORY SYNC ADDRESS switch in conjunction with the LOAD switch (see Controls and Indicators description, Section 3.1).

EXAMPLE: Assume the WORD MEMORY SYNC ADDRESS register equals 7 (000 000 000 111).

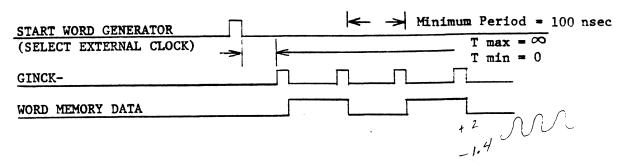

#### 3.2.4 Input Clock

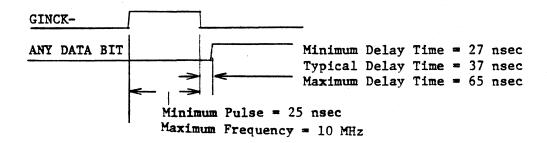

The gated input clock GINCK- enables an external device to clock the word generator. The word generator fetches a new word or shifts the output register on the negative edge (high-level to low-level transition \_\_\_\_) of each clock.

As shown in Figure 7, GINCK- must be in the low (zero) state when clocks are not generated to ensure that the RS-432 and the input clock will be synchronized on the first input clock, after the STL instruction. Otherwise, erroneous data may result for the first output word. All subsequent output words will be synchronized with GINCK-.

Figure 7. INPUT CLOCK RELATIONSHIP

Figure 8 portrays the input clock to output data timing relationship.

Figure 8. INPUT CLOCK/DATA OUT TIMING RELATIONSHIP

Note that the CLOCK IN signal available at the back panel BNC-type connector is identical to the input gated clock GINCK- on the 78-pin I/O connector. It is logically "ORed" with GINCK-. Thus, the same rules apply for this clock as for the input clock GINCK- discussed in the previous paragraph.

The CLOCK OUT and CLOCK IN signals permit two RS-432's to be run in parallel: for example, if 128 parallel data bits are required, two RS-432's with 64 parallel data bits each can be tied together, yielding 128 fully synchronous parallel data bits. This is accomplished by using one RS-432 as the master generator and the other as the slave. The master RS-432 starts its word generator selecting its internal period counter, and the slave starts the word generator selecting an external clock. The CLOCK OUT of the master RS-432 is then connected to the CLOCK IN of the slave RS-432. Note that a program "handshake" between the two machines must also be performed to ensure that the slave RS-432 is ready to transmit its data. This handshake is accomplished by using a flag from the slave machine to inform the master machine that it has started its word generator and is awaiting input clocks.

## 3.2.5 Output Data

This set of output signals consists of 16 parallel signal lines representing the data stored in an output register internal to the word generator section. The output register is fed from the word generator word memory in which user-defined data patterns or words have been prestored. Since the output register is also shift register, output data can be considered either parallel or serial. Serial shifting and parallel loading are controlled within the word generator via instructions from the microprocessor.

Available as options are additional output registers that can increase the total number of parallel output bits from 16 to 64. Note that standard on all RS-432's are all I/O control signals discussed in Sections 3.2.1 through 3.2.4, along with 16 output data lines. Output data lines 32 through 64 are optional. These additional data bits are also accessible via back panel connectors. Refer to the Appendix for their pin assignments. Refer to Figure 6, Figure 10, and Section 3.2.7 for timing relationships of these output signals.

## 3.2.6 Input Data

This set of optional input data bits consists of 16 or 32 parallel input data lines. These lines are routed internally to a set of digital compare circuits that indicate compare/no compare to values previously stored in the word generator memory. This input data is typically provided by the UUT in response to data and control signals previously provided by the RS-432. Bit masking capabilities exist to allow masking of input bits not pertinent to the go/no go comparison being made. Masking can be performed either manually via switches mounted on the input circuit card or dynamically via programmed microprocessor instructions.

Note that this input data section is an option to the basic RS-432. Check your specific RS-432 configuration for applicability. This option is provided with the comparator output wired to one of the input flag line, thus allowing the microprocessor to check the compare operation. Refer to Section 4.3 for a full explanation of the input compare option.

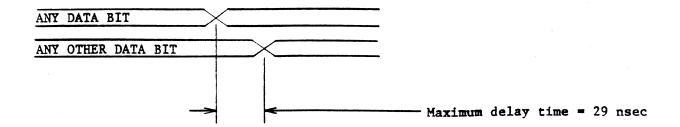

#### 3.2.7 Output Timing Relationship

Figure 9 shows the timing relationship of the rising edges of FEXCK+ and GEXCK+ with respect to any data from the word memory. The falling edges of FEXCK- and GEXCK- have similar timing delays to those of FEXCK+ and GEXCK+.

Figure 9. CLOCK/DATA TIMING RELATIONSHIP

Figure 10 shows the output timing relationship between any two data bits.

Figure 10. DATA TIMING RELATIONSHIP

## 3.2.8 Logic Ground

The logic ground signal is wired to the ground plane of the logic boards internal to the RS-432. This ground signal is not tied to the RS-432 chassis ground. The user may tie logic ground to chassis ground if desired.

#### 3.3 OPERATING PROCEDURE AND EXAMPLE

This section discusses operation of the RS-432 from the practical, "how to" application standpoint. It is presented to provide an overall view of the RS-432 and its application to any signal generation test problem. The section concludes with an example that can be loaded into and executed on any standard RS-432. Details of programming and circuit operation are covered in Section IV.

#### 3.3.1 Operating Procedure

Operation of the RS-432 involves several key steps: (1) problem definition and assignment of I/O signals, (2) program definition and writing, (3) program loading and execution (machine operation), (4) program debug/signal analysis, and (5) program documentation. Sequential progression through these steps assures a high probability of success with the least investment of time.

Problem definition yields such information as number of control signals and their timing requirements, number of parallel or serial output bits, output data rates, number of word memory locations required, where in word memory the data will reside, and other details required for programming. This information is used to assign the RS-432 inputs and outputs to the signal lines at the UUT with which they interface. This allows construction of a cabling arrangement to mate the RS-432 to the specific UUT. It also defines the signals that must be controlled by the microprocessor and word generator sections of the RS-432.

The second step, program definition, started during problem definition, where decisions were made concerning where and how the various signals were to be controlled. This step entails determining how the RS-432 program actually effects control of the I/O signals. Flow charting is a useful tool in finalizing the program definition in that it allows visualization of what steps the microprocessor must go through to accomplish its given task. The completed flow chart forms the skeleton of the detailed program that can then be written. The net result of a written program is normally a coding sheet filled with the machine language "1" and "0" that must be loaded into the RS-432. This step

also involves the generation of data or data patterns to be stored in the word memory.

Program loading, which consists of the transfer of machine language program into program memory, can be accomplished either manually via the front panel or under external control from a card reader, TTY, etc. (For manual entry refer to Section 3.1, Controls and Indicators, which describes the manual operation of the RS-432.) Upon completion of program loading, the program memory and word memory are loaded with their respective instructions and await execution.

Program execution and, thus, starting of the RS-432 signal generation, consists of placing the program memory address counter at the proper starting program memory address and depressing the START PROGRAM control switch. Depressing the STOP/CLEAR switch will immediately halt the RS-432, and clear all input pulse latches. The RS-432 can be started from this stopped state by depressing the START switch again.

Program debugging is aided by use of the SINGLE STEP switch and front panel LED readouts. The STEP switch allows single instruction steps to be taken with each switch activation for checking program logic and sequencing. Erroneous instructions or data words can be modified via the front panel.

Finally, when all signal generation tasks are accomplished, final program instructions, word memory patterns, and input/output waveforms must be documented. Interface Technology provides coding sheets to assist in the program development and documentation. These sheets appear in the Appendix and are used throughout this manual as examples.

## 3.3.2 RS-432 Example

The following example is presented to further acquaint the user with the operating procedure for the RS-432. Even though detailed explanations of the RS-432 program instructions have not been provided, the user can still use the coding sheets provided in this example, load the RS-432 program and word memory, and execute this example. His example also affords insight into the RS-432's capabilities, and is executable on any standard configuration RS-432.

## 3.3.2.1 Problem

Continuously output five 16-bit parallel words at a 300 millisecond-per-word rate if sense switch 0 is set. Set a control signal to indicate that the 300 millisecond data is being generated.

## 3.3.2.2 I/O Signals

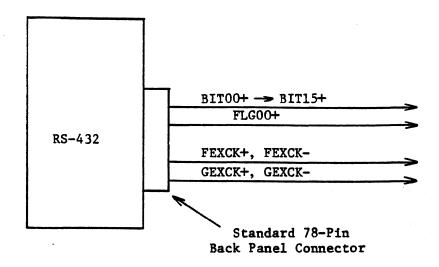

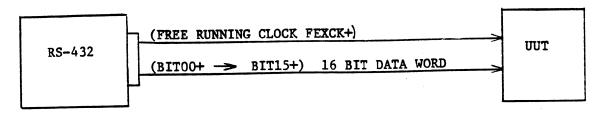

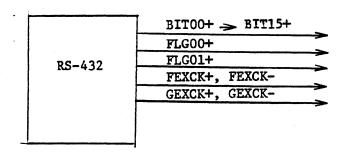

In this example, the 16 parallel bits will be generated on BIT00+ through BIT15 and the output control signals on FLG00+ and FLG01+. As a result of this program's execution, the following signals will also be generated:

- 1. Free running clock FEXCK+, FEXCK-

- 2. Gated clock GEXCK+, GEXCK-

When executing, the word generator can also generate the SYNC OUT signal at one of the five word memory addresses. Figure 11 depicts the RS-432 and the

various output signals. Refer to the Appendix for the pin assignments of these signals.

Figure 11. RS-432 I/O SIGNAL DIAGRAM FOR EXAMPLE

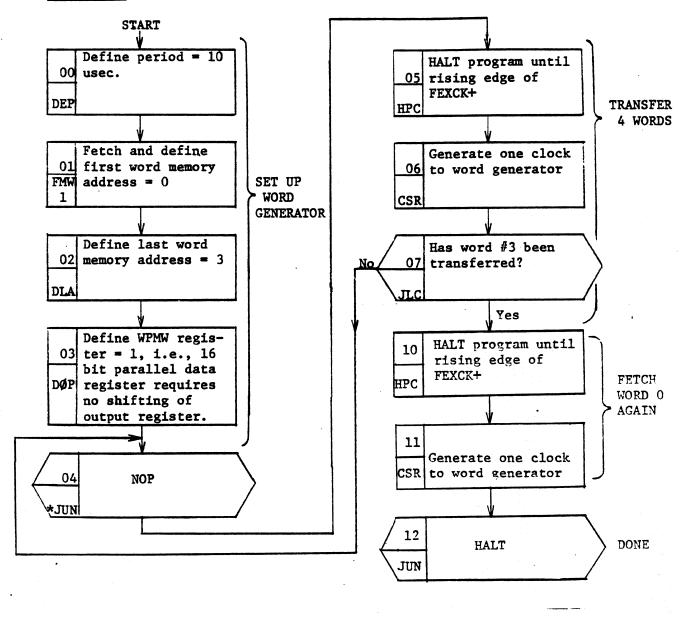

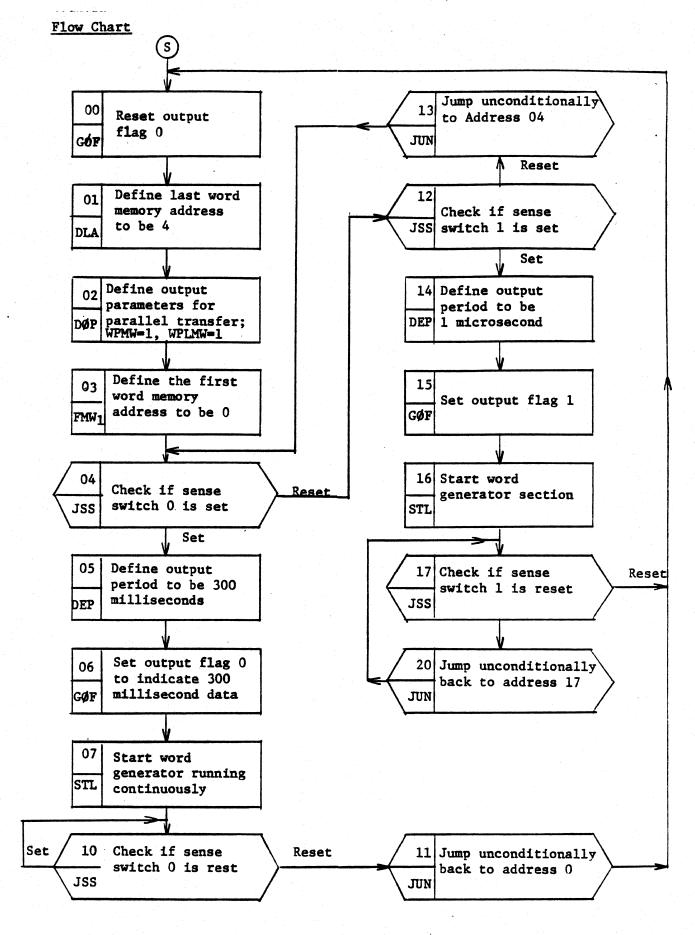

Refer to Figure 12 for a simplified flow chart of this example.

#### 3.3.2.3 Program Coding Sheet, Program Loading and Execution

Refer to Tables 4 and 5 for the program memory and word memory data coding sheets, respectively. By following instructions set forth in Section 3.1, Controls and Indicators, along with the program memory coding sheet and the word memory coding sheet, the RS-432 can manually be loaded. Once loaded, place the program memory address to location zero, reset all sense switches, and depress the START PROGRAM control switch.

The program will now be running and will be checking the sense switch; no data is being generated as the sense switch is not yet set. Setting Sense Switch 0 (SSO) and depressing the WORD MEMORY DATA 0-15 manual entry/display switch should allow visual verification that the five memory words are being generated at a rate of 300 milliseconds per word. Resetting SSO will stop the data transfer. The various output signals can be monitored on an oscilloscope. If the Sync Address register is loaded with the value 000, a synchronizing pulse occuring once every five words at word memory address 0 can be used to synchronize the oscilloscope. Note that at 300 milliseconds per word, one should be able to verify on the DATA LEDs the output pattern of Table 5.

Program Example 7: Parallel Data Transfer, Page 63, is a follow-up to this example. In it, the microprocessor will check two sense switches and generate data at one rate for Sense Switch 0, or generate data at a faster rate for Sense Switch 1. Program Example 7 should be programmed in lieu of this example if faster data rates are desired for oscilloscope monitoring of the output signals.

Figure 12. RS-432 FLOW CHART FOR EXAMPLE

| DATE: |    |  |  |

|-------|----|--|--|

|       |    |  |  |

| SHEET | OF |  |  |

Table 4: RS-432 PROGRAMMING SHEET (CODING)

| DDC             | PROGRAM NAME: RS-432 USER'S GUIDE EXAMPLE |                                     |                     |      |                                                                          |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    |                    |

|-----------------|-------------------------------------------|-------------------------------------|---------------------|------|--------------------------------------------------------------------------|------------|--------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------|-------------|---|----|--------------------|

| PRO             | JGK                                       | ATL                                 | I IN                | Hill | ╁                                                                        | -,,-       |              |                                                  |                                                  |                                                  | I            | NST                                              | RUC                                              | TIO                                              | 1                                                |                                                  |                                                  |                                                  |          |             |   |    |                    |

|                 | AD                                        | ADDRESS MNEMONIC OF CODE DATA FIELD |                     |      |                                                                          |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  | COMMENTS                                         |                                                  |          |             |   |    |                    |

|                 | 0                                         | CT                                  | AL                  |      | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br>GOF 0 / / 0 0 0 0 0 0 0 0 0 0 0 |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    |                    |

| $\vdash$        | 4                                         | $\dashv$                            | 0                   |      | 4                                                                        | GOF        | 0            |                                                  | $\vdash$                                         | 0                                                | 0            | 0                                                |                                                  | 9                                                |                                                  | 0                                                | 30                                               |                                                  | 0        | 0           |   | 00 | DGCG DAGAAA        |

|                 | $\dashv$                                  | -                                   | 00                  | 1 2  | +                                                                        | DLA<br>DOP | 14           | 00                                               | 0                                                | 10                                               | 00           | _                                                | 00                                               | 00                                               | 00                                               | 0                                                | 0                                                | 0                                                | 0        | 0           | 0 | )  | DEFINE PARAMETERS  |

| -               | $\dashv$                                  | ᅱ                                   | 8                   | 3    | ᅥ                                                                        | FMWI       | 7            | 0                                                | 7                                                | 1                                                | 0            | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0        |             | 0 |    |                    |

| <del> </del>    | 十                                         | ᅱ                                   | Ö                   | 4    | 1                                                                        | JSS        | O            |                                                  | 0                                                | 0                                                | 0            | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                |                                                  | 0        | 7           | _ | 0  | CHECK SEASE SWITCH |

|                 | 十                                         |                                     | Ö                   | 5    | 7                                                                        | DEP        | 1            | 0                                                | 0                                                | 0                                                | 0            | 0                                                | 0                                                | 7                                                | 0                                                | 0                                                | 7                                                | 0                                                | 1        | 1           |   | 0  | 1                  |

|                 |                                           |                                     |                     | 6    |                                                                          | GOF        | 0            | 1                                                | 1                                                | 0                                                | 0            |                                                  | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0        | 0           | 0 | 1  | START JOOMS DATA   |

|                 |                                           |                                     | 0                   | 7    |                                                                          | STL        | 1            | 1                                                | 1                                                | 0                                                | 0            | 1                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                |                                                  | 0        | 0           |   | 0  |                    |

|                 |                                           |                                     |                     | 0    |                                                                          | JLS        | 0            |                                                  | 0                                                | 0                                                | 0            | 0                                                | 1                                                | 0                                                | 0                                                | 0                                                | 0                                                |                                                  | 1        | 0           | 0 | _  | /                  |

|                 | _                                         |                                     | $\Box$              | 1    | 4                                                                        | JUN        | 0            | 1                                                | 0                                                | 0                                                | 0            | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0                                                | 0        | 0           | O | 0  | Jump Back          |

| $\vdash \vdash$ | 4                                         | _                                   | $\vdash \downarrow$ | 2    | 4                                                                        |            | <b>_</b>     |                                                  | _                                                |                                                  | _            |                                                  |                                                  |                                                  | _                                                | _                                                |                                                  |                                                  | $\vdash$ |             |   | -  |                    |

|                 | $\dashv$                                  | -                                   | 1                   | 3    | 4                                                                        |            | -            |                                                  | _                                                | -                                                | _            |                                                  | -                                                |                                                  | <del> </del>                                     | _                                                | <del> </del>                                     |                                                  | $\vdash$ |             | - | -  |                    |

| <b> </b>        | $\dashv$                                  | -                                   | 1                   | 5    | ᅱ                                                                        |            | -            |                                                  | -                                                | -                                                | -            | <u> </u>                                         | -                                                | -                                                | <del> </del>                                     |                                                  | $\vdash$                                         | <del>                                     </del> | $\vdash$ |             | _ |    |                    |

| ┠╼┼             | $\dashv$                                  | -                                   | +                   | 6    | +                                                                        |            | 1            | <del> </del>                                     | 1                                                | <del>                                     </del> | _            |                                                  |                                                  | _                                                | <del>                                     </del> | _                                                | $\vdash$                                         | -                                                | H        |             | - |    |                    |

| <b> -</b> -     | $\dashv$                                  | -                                   | +                   | 위    | ┪                                                                        |            | 1            | <del> </del>                                     | <del>                                     </del> | <del> </del>                                     | <b> </b>     |                                                  |                                                  | <b>-</b>                                         | <del> </del>                                     | <del>                                     </del> | 1                                                |                                                  | $\vdash$ | <del></del> |   |    |                    |

|                 | 十                                         | ᅱ                                   | <b>–</b>            | 0    | 1                                                                        |            | 1            | <del>                                     </del> | 1                                                |                                                  | -            | $\vdash$                                         | <del> </del>                                     |                                                  |                                                  |                                                  | 一                                                | 一                                                |          |             | _ |    |                    |

|                 | $\dashv$                                  |                                     |                     | 1    | 7                                                                        |            |              |                                                  | $\vdash$                                         |                                                  |              |                                                  | <b>-</b>                                         |                                                  |                                                  | 1                                                | 1                                                | Ì                                                |          |             |   |    |                    |

| $\Box$          | . 1                                       |                                     |                     | 2    | 7                                                                        |            | f            |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    |                    |

|                 | 寸                                         | ᅥ                                   |                     | 3    | 7                                                                        |            |              |                                                  | i T                                              |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    |                    |

|                 |                                           |                                     |                     | 4    |                                                                          |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    |                    |

|                 |                                           |                                     |                     | 5    |                                                                          |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    | ·                  |

|                 |                                           |                                     |                     | 6    |                                                                          |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |             |   |    |                    |

| $\sqcup$        | _                                         | _                                   |                     | 7    | _                                                                        |            |              |                                                  |                                                  |                                                  |              |                                                  |                                                  |                                                  |                                                  |                                                  | _                                                |                                                  |          |             |   |    |                    |

| $\sqcup$        | _                                         | _                                   |                     | 0    | 4                                                                        |            | _            |                                                  |                                                  |                                                  |              |                                                  | _                                                |                                                  |                                                  |                                                  | <u> </u>                                         |                                                  |          |             |   |    |                    |

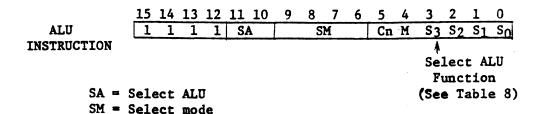

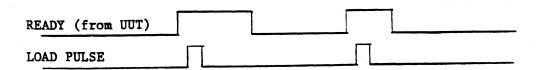

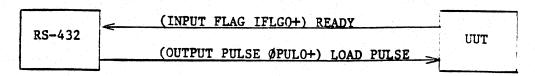

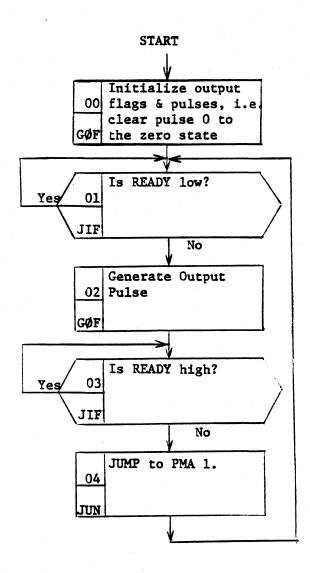

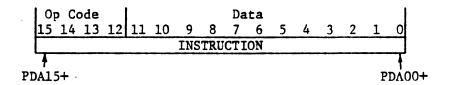

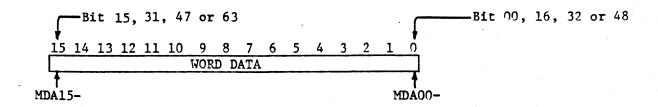

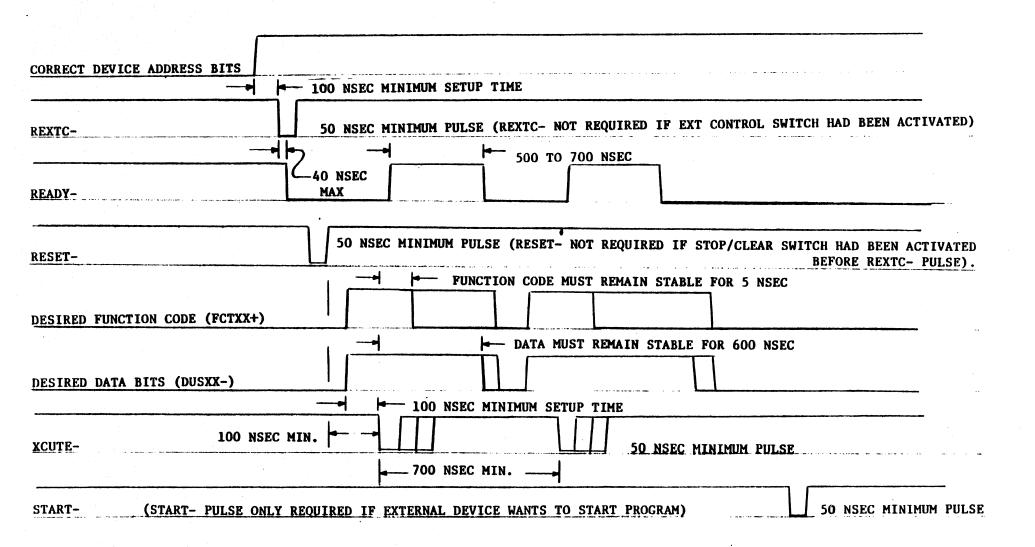

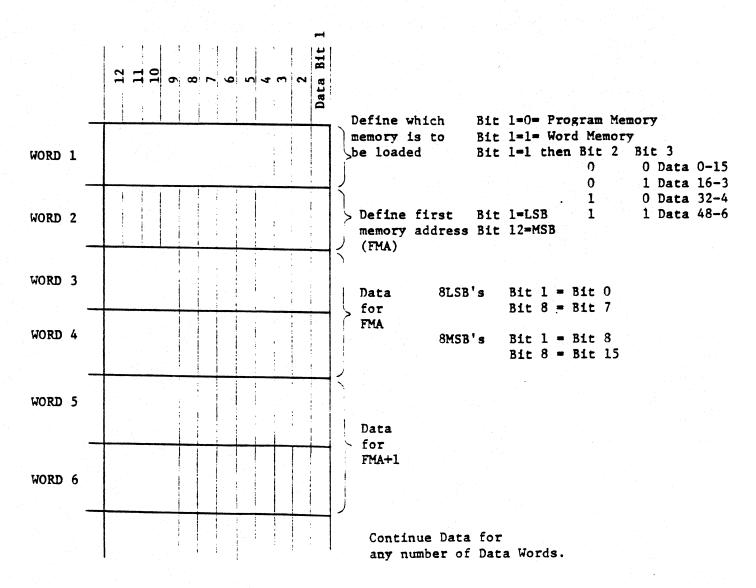

| -               | -                                         | _                                   |                     | 1    | 4                                                                        |            | <u> </u>     |                                                  | <u> </u>                                         | <u> </u>                                         | _            |                                                  | _                                                |                                                  |                                                  |                                                  | <u> </u>                                         | <u> </u>                                         |          |             |   |    |                    |