# Q/DH Controller User's Guide

10177X07

October 1982

ABLE Computer 1751 Langley Avenue Irvine, California 92714 (714) 979-7030 TWX 910-595-1729

October 1982

The material in this manual is for informational purposes and is subject to change without notice.

DEC, PDP and Q Bus are trademarks of Digital Equipment Corporation.

Q/DH is a trademark of ABLE Computer.

# CONTENTS

| SECTION 1 | HOW TO USE THIS MANUAL 1-1                                                                                                                                     |      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| SECTION 2 | WHAT IS Q/DH                                                                                                                                                   |      |

|           | <pre>2.1 GENERAL DESCRIPTION</pre>                                                                                                                             |      |

| SECTION 3 | HOW TO INSTALL Q/DH                                                                                                                                            |      |

| •         | 3.1INSTALLATION PROCEDURE.3-13.2UNPACKING THE Q/DH.3-23.3VERIFY THAT YOU RECEIVED WHAT YOU<br>ORDERED3-2                                                       |      |

|           | 3.4 EQUIPMENT NEEDED TO USE THE Q/DH 3-2<br>3.5 HOW TO DETERMINE ADDRESS AND VECTOR<br>ASSIGNMENTS                                                             |      |

|           | 3.6 HOW TO SET THE DEVICE ADDRESS AND<br>VECTOR SELECTION SWITCHES                                                                                             |      |

|           | 3.6.5 Miscellaneous Functions 3-9<br>3.7 MAINTENANCE FEATURES                                                                                                  |      |

|           | 3.8 PRIORITY SELECTION                                                                                                                                         | ļ    |

|           | SYSTEM.       3-14         3.11 INSTALLATION VERIFICATION       3-14         3.11.1 ZDHM Diagnostics       3-14         3.11.2 Internal Diagnostics       3-15 | <br> |

PAGE 3

| SECTION | 4   | WHAT       | TO DO                              | IF Q                      | / DH                         | DOES                       | NO                   | TW                | ORK               | •          | •••        | •   | •   | • | 4-1                |

|---------|-----|------------|------------------------------------|---------------------------|------------------------------|----------------------------|----------------------|-------------------|-------------------|------------|------------|-----|-----|---|--------------------|

|         |     | 4.1<br>4.2 | HOW TO<br>TROUBL<br>4.2.1<br>4.2.2 | ESHO<br>LED               | OTIN<br>s On                 | IG TI                      | PS.                  | •                 | • •               | •          | •••        | •   | é   | • | 4-2                |

|         |     | 4.3        | CUSTON<br>4.3.1                    | Inst<br>IER SI<br>Who     | tall<br>ERVC<br>to           | atic<br>IE.<br>Call        | fo                   | r S               | erv:              | ice        | <br><br>wi | thi | .n  | • | -                  |

|         |     |            | 4.3.2                              | Who                       | to                           | ted<br>Call<br>ted         | fo                   | r S               | ervi              | ice        | où         | tsi | de  |   | -                  |

|         | •   |            |                                    | Unc                       | 0111                         |                            | Dua                  |                   | ••                | •          | • •        | •   | •   | • | - <b></b>          |

| SECTION | 5   | 5.1        | TYPICA<br>TERMIN                   | L AP                      | PLIC<br>OMMU                 | CATIC<br>INICA             | NS.<br>TIO           | NS                | LINI              | K.         | •••        | •   | •   | • | 5-1                |

|         |     | 5.3        | INTERF<br>Q/BUS                    | CONNI                     | INFC                         | ORMAI<br>OR IN             | FOR                  | MAT               | ION               | •          | •••        | •   | •   | • | 5-1<br>5-2         |

|         |     |            |                                    |                           |                              |                            |                      |                   |                   |            |            |     |     |   |                    |

| SECTION | 6   | HOW        | TO PROC                            | GRAM                      | Q/DH                         | I                          | •                    | •                 | • •               | •          | •••        | •   | •   | • | 6-1                |

|         |     | 6.1        | DATA H<br>6.1.1<br>6.1.2           | Syst                      | tem                          | REGI<br>Cont<br>ceiv       | rol                  | Re                | gist              | cer        |            |     |     |   |                    |

|         |     |            | 6.1.3<br>6.1.4                     | Reg:<br>Lin               | iste<br>e Pa                 | er ()<br>irame             | (02)<br>eter         | Re                | gist              | cer        | ( X        | 04) | •   | • | 6-7<br>6-8<br>6-10 |

|         |     |            | 6.1.5<br>6.1.6<br>6.1.7            | Byt<br>Buf<br>Bre         | e Co<br>fer<br>ak (          | ount<br>Acti               | Reg<br>ve            | ist<br>Reg<br>Tim | er<br>isto<br>ing | (X1)<br>er | )).<br>• • | •   | •   | • | 6-11<br>6-11       |

|         |     | 6.2        | 6.1.8<br>MODEM<br>6.2.1            | Reg<br>Sil<br>REGI<br>Con | iste<br>o St<br>STEF<br>trol | er ()<br>atus<br>RS<br>and | (14)<br>8 Re<br>1 St | gis<br>atu        | ter<br>s Re       | egi:       | <br>ste    | r.  | •   | • | 6-13               |

|         | · . | 6.3        | 6.2.2<br>TRANSM<br>CONSII          | IITTE                     | R/RE                         | ECEIN                      | IER                  | SPE               | ED 1              | PRO        | GRA        | MM  | ENC | ľ |                    |

|         |     | 6.5        | BREAK<br>TRANSN                    | CONT<br>11TTE             | ROL<br>R AN                  | TIMI<br>ID RI              | ING.<br>ECEI         | VER               | TI                | MIN        | <br>G      | •   | •   | • | 6-19               |

|         |     | 6.6        | CONSII<br>MAINTI                   | ENANC                     | IONS<br>E MC                 | DDE (                      | CONS                 | IDE               | RAT               | ion        | s.         | •   | •   | • | 6-20<br>6-20       |

|         |     |            |                                    | •                         |                              |                            |                      |                   |                   |            |            |     |     |   |                    |

| SECTION | 7   |            |                                    |                           |                              |                            | • •                  | •                 | • •               | •          | ••         | •   |     |   | 7-1                |

|         |     | (•1<br>7•2 | ARCHI'<br>ASYNCI                   | IRONO                     | KE.<br>US S                  | SERI                       | AL L                 | INE               | IN                | TER        | FAC        | ES  | •   | • | 7-1<br>7-2         |

|            | <ul> <li>7.3 MICROPROGRAM ARCHITECTURE</li></ul> |  |

|------------|--------------------------------------------------|--|

| APPENDIX A | DH AND DM ADDRESS SWITCH SETTINGS A-1            |  |

| APPENDIX B | DH AND DM VECTOR SWITCH SETTINGS B-1             |  |

| APPENDIX C | PRIORITY STRAPPING                               |  |

| APPENDIX D | VOLTAGE SOURCES ON THE BACKPLANE D-1             |  |

| APPENDIX E | SPARE PARTS LIST                                 |  |

| APPENDIX F | LIST OF MATERIALS                                |  |

× .

# LIST OF FIGURES

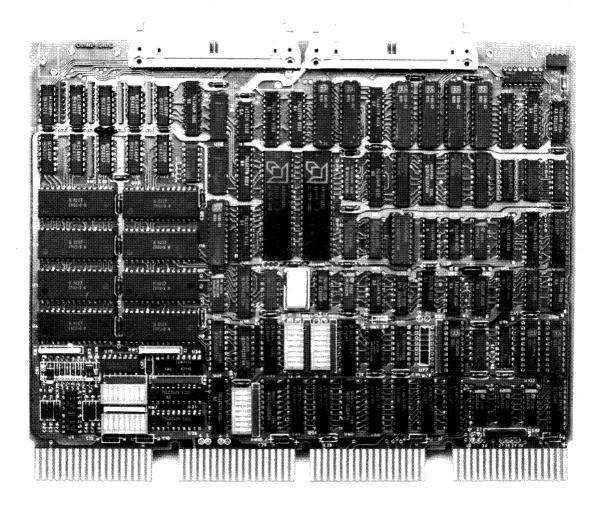

| 2-1 | Q/DH PC Controller Model 10176 2              | 2-2                                                                           |

|-----|-----------------------------------------------|-------------------------------------------------------------------------------|

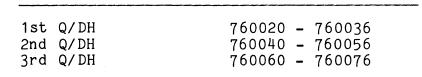

| 3-1 | Q/DH Board Layout                             | 3-3                                                                           |

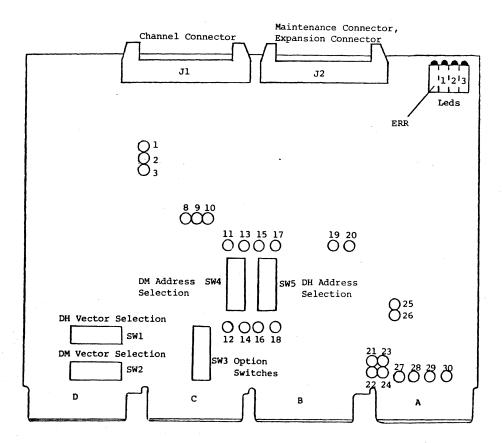

| 3-2 | Address Map                                   | 3-4                                                                           |

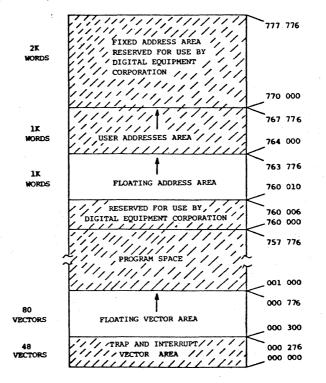

| 3-3 | Q/DH Switch Descriptions 3                    | 5-8                                                                           |

| 5-1 | Q/DH Applications 5                           | j-2                                                                           |

| 6-1 | Data Handling Registers 6                     | <b>j-</b> 3                                                                   |

| 6-2 | Data Handling Register Formats 6              | -4                                                                            |

| 6-3 | Modem Registers 6                             | 5-14                                                                          |

| 6-4 | Modem Register Formats 6                      | i <b>-</b> 15                                                                 |

|     | 3-1<br>3-2<br>3-3<br>5-1<br>6-1<br>6-2<br>6-3 | 3-3Q/DH Switch Descriptions.35-1Q/DH Applications56-1Data Handling Registers6 |

# LIST OF TABLES

| Table 3-1              | Device Ranks for Floating Address Assignment 3-5 |

|------------------------|--------------------------------------------------|

| Table 3 <del>-</del> 2 | Floating Interrupt Vector Devices 3-6            |

| Table 3-3              | Typical Vector Addresses                         |

| Table 3-4              | Switch S3 Functions                              |

| Table 3-5              | Maintenance Switch Settings                      |

| Table 3-6              | Microdiagnostic Execution Chart                  |

| Table 3-7              | Maintenance Display Chart                        |

| Table 3-8              | Patches to ZDHM Diagnostic                       |

| Table 5-1              | Connectors on Q/DH Controller                    |

| Table 5-2              | Q/DH Controller Connector A                      |

|                        | Pin Assignments                                  |

| Table 5-3              | Q/DH Controller Connector B                      |

|                        | Pin Assignments                                  |

| Table 5-4              | Q/DH Controller Connector C                      |

|                        | Pin Assignments                                  |

| Table 5-5              | Q/DH Controller Connector D                      |

|                        | Pin Assignments                                  |

| Table 6-1              | Data Handling Register List 6-2                  |

|                        | Transmitter Baud Rate                            |

|                        |                                                  |

r

# CHAPTER 1

# How To Use This Manual

Congratulations on your purchase of a Q/DH from ABLE Computer. We are sure it will provide you with years of satisfactory service. We have prepared this manual to help you maximize the effectiveness of the Q/DH in your system. This manual is provided to assist you with the installation, use and care of Q/DH; it does not provide repair information. If you have problems with your Q/DH, we prefer that you let us repair it in our factory. This manual assumes that you are familiar with the LSI-11 architecture and Q Bus structure. For information about the LSI-11, refer to the following DEC documents:

- \* Microcomputers and Memories Handbook

- \* Microcomputer Interfaces Handbook

For information about the Q Bus, refer to the following DEC documents:

- \* Microcomputers and Memories Handbook

- \* PDP-11 Bus Handbook

You may also wish to refer to the following ABLE documents for Q/DH system information:

- \* <u>ABLE Q/DH</u> <u>Subsystem</u> <u>User's</u> <u>Guide</u>, document number 10180X07

- \* <u>ABLE Dual Purpose Distribution Panel User's Guide</u>, document number 10129X07

This manual is organized into the following chapters:

\* Chapter 2 contains general description of Q/DH and lists its special features. It also includes programmable line parameter information, electrical specifications, and physical specifications. Photographs of the Q/DH are included in this chapter.

# How To Use This Manual

PAGE 1-2

- \* Chapter 3 contains detailed instructions on installation. The functions of all switches on the board are described. Information on maintenance features, including microdiagnostics is also contained in this chapter.

- \* Chapter 4 contains information on the care of Q/DH and troubleshooting tips in the event that a problem occurs. The procedure for obtaining assistance form ABLE Computer is also described.

- Chapter 5 describes a typical application for Q/DH. Terminal/communications information, wiring information for modem connection, and Q Bus connector information is also provided.

- \* Chapter 6 contains descriptions of data handling registers, modem registers, timing considerations for transmitter/receiver speed programming, break control, and transmitter and receiver timing. Maintenance mode considerations are also provided.

- \* Chapter 7 describes on how Q/DH works. Message transmission and reception, modem control, ring signal application, baud rate selection and the diagnostic microprOgram, are described.

- The appendices provide an interrupt level strapping chart to alter the priority level of Q/DH and loopback connection information.

The appendices contain a spare parts listing for those wishing to maintain a spare parts inventory and also a list of materials for the Q/DH.

# CHAPTER 2

# What Is Q/DH?

# 2.1 GENERAL DESCRIPTION

The Q/DH is a microprocessor-based controller which connects a Q Bus system to 8 or 16 asynchronous communications lines. It provides DMA (direct memory acess) output capabilities and modem control. It is system software compatible with the DEC DH11 and DM11-BB. An 8 line Q/DH can be installed in any standard quad Q Bus backplane. A 16 line Q/DH requires two quad slots. See Figure 2-1.

# 2.2 FEATURES

- \* DMA capability provides significant system throughput improvement over interrupt-driven devices.

- \* Large input silo improves input handling capacity which reduces data overrun probability for block mode terminals and computer-to-computer interconnects.

- \* Word DMA output transfers allow optimum Q Bus utilization.

- \* Operating system software compatible with DEC DH and DM.

- \* On-board pencil switches for address and vector selection add flexibility and eliminate jumpers.

\* Comprehensive self-test diagnostic with LED display.

Available with EIA panel or with a line adapter/panel which offers both EIA and 20ma current loop channels.

- \* Diagnostic loopback connectors are built into optional distribution panels.

- \* Provides interface and signals conforming to EIA RS-232-C standards.

- Modem events reported under interrupt control to eliminate system overhead associated with DZV11-style modem scanning.

Figure 2-1: Q/DH Controller Model 10176

What Is Q/DH?

# 2.3 SPECIFICATIONS

2.3.1 Programmable Line Parameters

Character Length: 5, 6, 7, or 8 data bits

Number of Stop bits:

data bits 1 or 2 for 6-,

7-, or 8- bit characters; 1 or 1.5 for 5-bit characters

Odd, even, or none

Full duplex

Parity Generation/Detection:

Operating Modes:

Transmitter/Receiver Speeds (Baud):

0, 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2400, 4800, 9600, plus 19200 (replacing External A)

# 2.3.2 Electrical Specifications

Bus Loading:

# Controller

DC Loads: 1 AC Loads: 2

Expander Board

| DC | Loads: | 0 |

|----|--------|---|

| AC | Loads: | 2 |

Power Requirements:

Controller

5.0 amps at +5V 0.35 amps at +12V

Expander Board

1.5 amps at +5V 0.35 amps at +12V

Interrupt Request Level: DH function is set at BR5. DM function is set at BR4. Priority levels may be user-modified.

2.3.3 Modem Control

For each line, the Q/DH moniters two data set output control signals, ring and carrier, and controls one data set input control signal, Data Terminal Ready.

2.3.4 Addressing

Device Address:

The Q/DH requires eight consecutive word addresses in the floating address space which starts at 760010. All Q/DH units in a system should have consecutive word addresses.

The modem control requires two consecutive word addresses, the first of which must be a multiple of four. Address space has been assigned for 16 Q/DH Controllers. The first is at 770500; the second starts at 770510, and so forth.

Interrupt Vectors:

The Q/DH requires three interrupt vectors, two consecutive vectors XXO and XX4, are for the receiver and the transmitter respectively. A separate vector, XXX, is for the modem. These are in the floating vector space (300 -776).

# 2.3.5 Physical Specifications

Board Size:

The Q/DH Controller is a standard quad-width board. Rectangular dimensions are 10.45 inches (26.5 cm) x 8.40 inches (21.3 cm). The board is shown in Figure 2-1.

The Q/DH Expander board is also a quad-width board.

•

.

# CHAPTER 3

# How To Install Q/DH

# 3.1 INSTALLATION PROCEDURE

This chapter explains in detail how to install Q/DH. Below is a brief, step-by-step procedure.

- 1. Determine the address assignment of the DM portion and set switch S4 accordingly (Section 3.5 and Section 3.6.1).

- 2. Determine the address assignment of the DH portion and set switch S5 accordingly (Section 3.5 and Section 3.6.2).

- 3. Determine the vector assignment of the DM portion and set switch S2 accordingly (Section 3.5 and Section 3.6.3).

- 4. Determine the vector assignment of the DH portion and set switch S1 accordingly (Section 3.5 and Section 3.6.4).

- 5. Refer to Table 3-4 for switch S3 functions and set the switch accordingly (Section 3.7.1).

- 6. Set maintenance switches to achieve the desired functions (Section 3.7.1).

- If interrupt levels other than the ones factory set are required, modify the jumper connections (Section 3.8).

- 8. Remove power from the system (Section 3.9).

- 9. Install Q/DH board in vacant slot (Section 3.10).

- 10. Check that there are no vacant slots between the Q/DH and the CPU.

- Apply power to the system, checking the LEDs to verify internal operation of the board (Section 3.12).

- 12. Run the diagnostics (Section 3.11).

# 3.2 UNPACKING THE Q/DH

The Q/DH is shipped in a special container to prevent damage during shipment. It is recommended that this container be saved for use in the event that the product requires subsequent reshipment. Unpack the contents carefully and inspect for any signs of damage. If damage is found, notify the carrier immediately.

# 3.3 VERIFY THAT YOU RECEIVED WHAT YOU ORDERED

Be sure that you received what you ordered by checking the board numbers. Q/DH has two numbers found on the backside of the board in the upper right corner: 10176 (etched) and 10177 (stamped). See Figure 3-1. The expander board has 10176 (etched) and 10178 (stamped) on the board.

# 3.4 EQUIPMENT NEEDED TO USE THE Q/DH

You will need the following equipment to use the Q/DH:

- \* LSI-11 Q Bus computer system

- \* One vacant quad slot for mounting the Q/DH for an 8 line, or two vacant quad slots for a 16 line.

- \* Sufficient power

# How To Install Q/DH

PAGE 3-3

# 3.5 HOW TO DETERMINE ADDRESS AND VECTOR ASSIGNMENTS

The DH portion of the Q/DH uses eight words of floating address space. The floating address space begins at 760010 as shown in Figure 3-2. Addresses within this space are assigned according to rank. Table 3-1 shows the ranks assigned to devices addressed in this range.

The DH uses addresses located after any DJ11's in the system. Each DH requires eight consecutive addresses starting with an address that is a multiple of 20 (octal). For example, for a system with no DJ11 units, register address assignments for three Q/DH units are as follows: Unit Octal Register Address

Figure 3-1: Q/DH Board Layout

Figure 3-2: Address Map

Notice that, although the system in this example contains no DJ11 units, address 760010 cannot be assigned to the first Q/DH unit because it is not a multiple of 20 (octal).

| Rank | Unibus Device | Q Bus Device  |

|------|---------------|---------------|

| 1    | DJ 1 1        |               |

| 2    | DH 11,        | Q/DH          |

| 3    | DQ11<br>DU11  | DUV11         |

| 5    | DPU11         |               |

| 6    | LK11A         |               |

| 7    | DMC11,DMR11   |               |

| 8    | DZ11, DZ/16   | DZ V 1 1      |

| 9    | KMC11         |               |

| 10   | RL11 (extra)  | RLV11 (extra) |

|      |               |               |

Table 3-1: Device Ranks for Floating Address Assignment

The DM portion of the Q/DH requires two additional consecutive word addresses. Available address space is from 770000 through 773770. The addresses assigned to the registers of the first DM in a system are 770500 and 770502. The addresses for additional DM registers start at consecutive addresses which are multiples of 10 (octal). Thus, the addresses for a second DM are 770510 and 770512; those for a third DM are 770520 and 770522; and so on.

The DH uses two interrupt vectors (for the receiver and transmitter interrupts). The DM uses one interrupt vector. Vector addresses for all devices are assigned in order from 300 through 774 according to the DEC rankings listed in Table 3-2. Find the device in your system with the lowest rank number and assign this 300, etc. Next find the device with the second lowest rank number and assign it the next consecutive vector address. Continue until all vector addresses are assigned. If a device is added to an existing system, its vector address must be inserted at the normal position and all other device addresses incremented accordingly. Table 3-3 shows the sample vector addresses for the Q/DH.

# How To Install Q/DH

# PAGE 3-6

| NUMBER                | DEVICE TYPE                      | Q BUS DEVICE                    |

|-----------------------|----------------------------------|---------------------------------|

| 1                     | DC11                             |                                 |

| 2<br>3<br>4<br>5<br>6 | KL11, DL11-A,B, QUAD/B<br>DP11   | DLV11,-F,-J                     |

| 4                     | DM 1 1 – A                       |                                 |

| 5                     | QUADRACALL, DN11                 | Madam of O(DU                   |

| 0                     | DM11-BB,                         | $\frac{Modem}{of} \frac{Q}{DH}$ |

| 7                     | DR 1 1 – A                       | DRV11-B                         |

| 7<br>8<br>9           | DR11-C, DUAL I/O<br>PA611 Reader | DRV11                           |

| 10                    | PA611 Punch                      |                                 |

| 11                    | DT 1 1                           |                                 |

| 12<br>13              | DX11<br>DL11-C,D,E, QUAD/C,E     | DLV11-E                         |

| 14                    | DJ11                             |                                 |

| 15                    | DH11, DH/DM                      | Q/DH                            |

| 16<br>17              | GT40<br>LPS11                    |                                 |

| 18                    | DQ11                             |                                 |

| 19                    | KW 1 1 – W                       | KWV11                           |

| 20                    | DU 1 1                           | DUV11                           |

|                       |                                  |                                 |

Table 3-2: Floating Interrupt Vector Device

| Device               | Channels         | Vector                  |            |

|----------------------|------------------|-------------------------|------------|

| <br>1st DM<br>2nd DM | 0 - 15<br>0 - 15 |                         | 300<br>304 |

| <br>1st DH           | 0 - 15           | Receiver<br>Transmitter | 310<br>314 |

| 2nd DH               | 0 - 15           | Receiver<br>Transmitter | 320<br>324 |

Table 3-3: Typical Vector Addresses

# 3.6 HOW TO SET THE DEVICE ADDRESS AND VECTOR SELECTION SWITCHES

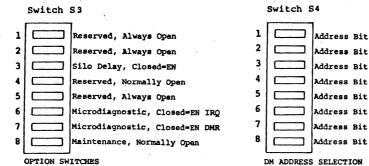

# 3.6.1 DM Device Address Switch (S4)

Device addresses for the DM portion of the Q/DH are set using switch S4 on the board. Refer to Figure 3-1 for the location of switch S4 and Figure 3-3 for switch descriptions. Use Appendix A to determine the device address switch settings. The starting address can be determined by referring to the information in Section 3.5.

# 3.6.2 DH Device Address Switch (S5)

Device addresses for the DH portion of the Q/DH are set using switch S5. Refer to Figure 3-1 for the location of switch S5 and Figure 3-3 for switch descriptions. Use Appendix A to determine the device address switch settings. The starting address can be determined by referring to the information in Section 3.5.

# NOTE

An open switch is accomplished by pressing the side of the switch marked "OPEN."

## 3.6.3 DM Vector Address Switch (S2)

Vector addresses for the DM portion of the Q/DH are set using switch S2. Refer to Figure 3-1 for the location of switch S2 on the board and Figure 3-3 for switch descriptions. Use Appendix B to determine the vector address switch settings. Section 3.5 describes how to determine the desired vector addresses.

# How To Install Q/DH

#### Switch S1 Switch S2 1 1 Vector Bit 08 Г Г Vector Bit 08 Microdiagnostic, Option SW1 2 2 Microdiagnostic, Option SW3 L 3 Microdiagnostic, Option SW2 3 Vector Bit 02 ٢ Г ٦ 4 Vector Bit 03 4 Vector Bit 03 Г 5 Vector Bit 04 5 Vector Bit 04 C Е 6 6 Vector Bit 05 Vector Bit 05 ſ 7 7 Vector Bit 06 Vector Bit 06 8 8 Vector Bit 07 Vector Bit 07 ٢ ſ DH VECTOR SELECTION DM VECTOR SELECTION

# Figure 3-3: Q/DH Switch Descriptions

Address Bit 03 Address Bit 04 Address Bit 05 Address Bit 06 Address Bit 07 Address Bit 08 Address Bit 09 Address Bit 10

PAGE 3-8

PAGE 3-9

3.6.4 DH Vector Address Switch (S1)

Vector addresses for the DH portion of the Q/DH are set using switch S1 on the board. Refer to Figure 3-1 for the location of switch S1 and Figure 3-3 for switch descriptions. Use Appendix B to determine the vector address switch settings. To determine the desired vector addresses refer to Section 3.5.

3.6.5 Miscellaneous Functions

Switch S4 contains a variety of functions for the Q/DH. Appendix B lists these functions.

# 3.7 MAINTENANCE FEATURES

# 3.7.1 Maintenance Features

For maintenance purposes, there are six switch positions which control the resident microcoded diagnostic for the Q/DH. Refer to Table 3-4 for definitions and functions of these switches. Table 3-7 lists the execution sequence of the microdiagnostic.

For normal operation, set the switches as follows:

Switch S1, position 2 - Closed Switch S1, position 3 - Open Switch S2, position 2 - Open Switch S3, position 6 - Open Switch S3, position 7 - Open Switch S3, position 8 - Open

| Switch S3<br>Position | Function                                                                                                                                                                                                                                                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2                | Not Used.<br>Not Used.                                                                                                                                                                                                                                                                                                   |

| 3                     | When closed, enables the silo delay feature.<br>The receiver interrupt is delayed by about<br>20ms if there are fewer than 16 characters<br>in the input silo. This reduces the number<br>of interrupts when a line is used as a link<br>to another computer. When open, this<br>switch disables the silo delay feature. |

| 4                     | When open, transmission on a line is<br>terminated in a manner identical to the<br>DH11. When closed, a zero byte count will<br>always terminate transmission on a line.                                                                                                                                                 |

| 5                     | Not Used.                                                                                                                                                                                                                                                                                                                |

| 6                     | When closed, this switch runs the IRQ<br>micro-test if in microdiagnostic<br>maintenance mode.                                                                                                                                                                                                                           |

| 7                     | When closed, runs the DMR micro-test if in microdiagnostic maintenance mode.                                                                                                                                                                                                                                             |

| 8                     | This switch is closed to disable the cable<br>maintenance mode. It is normally open<br>except when the Q/DH is used without an<br>ABLE distribution panel.                                                                                                                                                               |

How To Install Q/DH

| Switch        | Setting | Function                                                                                                                                              |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| S2-2          |         | LOOP ON MICRODIAGNOSTIC (NO EMULATION)                                                                                                                |

|               | Open    | Runs the microdiagnostic on power-up and exits to emulation when done.                                                                                |

|               | Closed  | Remains in the microdiagnostic on power-up.                                                                                                           |

| S1 <b>-</b> 2 |         | HANG ON SECTION IN ERROR                                                                                                                              |

|               | Open    | Microdiagnostic continues when an error is encountered.                                                                                               |

|               | Closed  | Microdiagnostic hangs when an error is encountered.                                                                                                   |

| S1 <b>-</b> 3 |         | LOOP ON SECTION                                                                                                                                       |

|               | Open    | Advances to next section at end of each section.                                                                                                      |

|               | Closed  | Remains in current section is S6-1 is closed.                                                                                                         |

| S3-6          |         | RUN IRQ TEST                                                                                                                                          |

| •             | Open    | IRQ test will not be run.                                                                                                                             |

|               | Closed  | IRQ test will be run if LOOP ON<br>MICRODIAGNOSTIC is set.                                                                                            |

| S3-7          |         | RUN DMR TEST                                                                                                                                          |

| •             | Open    | DMR test will not be run.                                                                                                                             |

|               | Closed  | DMR test will be run if LOOP ON<br>MICRODIAGNOSTIC is set.                                                                                            |

| S3-8          |         | CABLE MAINTENANCE DISABLE                                                                                                                             |

|               | Open    | Allows microdiagnostic to detect when<br>cables are installed in maintenance<br>position. Will allow UART TEST to check<br>EIA drivers and receivers. |

|               | Closed  | UART TEST will use internal loop-backs.                                                                                                               |

Table 3-5: Maintenance Switch Settings (See notes on the following page.)

| NOTE: |                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.    | Bus and UART section are bypassed when switches are set<br>to proceed into emulation due to the time required to<br>perform the UART test, and because the Bus tests may<br>disturb the system. |

| 2.    | Any error detected in the first section of the<br>microdiagnostic will cause a hang regardless of the<br>switch settings.                                                                       |

| 3.    | The "ERR" indicator is reset at the beginning of each section of the microdiagnostic.                                                                                                           |

| 4.    | When running the bus tests, a "BR" instruction (777 octal) should be executed at location zero.                                                                                                 |

|       |                                                                                                                                                                                                 |

| EXECUTION<br>SEQUENCE | SECTION (as encoded in LEDs)                                                                                            |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| Power Up<br>1<br>2    | Section 7 - SEQ<br>Section 3 - DATA                                                                                     |

| 3<br>4<br>5           | (2901)<br>Section 1 - DBIT<br>Section 5 - PROM<br>Section 4 - BUF                                                       |

| 6                     | Section 6 - BUS<br>(DMR, IRQ)                                                                                           |

| 7                     | Section 2 - UART<br>If S2-2 is open,<br>Section 6 and 2 are<br>bypassed and<br>emulation is entered<br>after Section 4. |

Table 3-6: Microdiagnostic Execution Chart

PAGE 3-13

# 3.7.2 Maintenance Display

The Q/DH contains four LEDs for maintenance display purposes. These LEDs are located at the top of the board. Figure 3-1 shows the location of the LEDs. Refer to Table 3-7 for descriptions of the LED displays. Section 3.12 provides more information on the LEDs.

| ERR                                           | DISPL<br>1                                       | AY<br>2                                         | 3                                                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| off<br>off<br>off<br>off<br>off<br>off        | off<br>off<br>off<br>off<br>on<br>on<br>on       |                                                 | off<br>on<br>off<br>on<br>off<br>on<br>off             | END PASS/ EMULATION<br>Testing Section 1 - DBIT<br>Testing Section 2 - UART<br>Testing Section 3 - DATA (2901)<br>Testing Section 4 - BUF<br>Testing Section 5 - PROM<br>Testing Section 6 - BUS                                                                                                                               |

| off<br>on<br>on<br>on<br>on<br>on<br>on<br>on | on<br>off<br>off<br>off<br>off<br>on<br>on<br>on | on<br>off<br>on<br>on<br>off<br>off<br>on<br>on | on<br>off<br>on<br>off<br>on<br>off<br>on<br>off<br>on | (DMR, IRQ)<br>Testing Section 7 - SEQ<br>Error - Undefined problem<br>Error in Section 1 - DBIT Error<br>Error in Section 2 - UART Error<br>Error in Section 3 - DATA (2901)<br>Error<br>Error in Section 4 - BUF Error<br>Error in Section 5 - PROM Error<br>Error in Section 6 - BUS Error<br>Error in Section 7 - SEQ Error |

Table 3-7: Maintenance Display Chart

# 3.8 PRIORITY SELECTION

The standard priority interrupt levels for the Q/DH are IRQ5 for the DH and IRQ4 for the DM. These levels are factory wired and require no user adjustment.

If you wish to change interrupt levels for the DH or DM, use the strapping chart in Appendix C.

# How To Install Q/DH

PAGE 3-14

# 3.9 PREPARING YOUR SYSTEM FOR THE Q/DH

To prepare your system for installing the Q/DH, remove power from the system. Use either the front panel switch or the master breaker switch. We suggest that both switches be turned off.

Once power is removed from the system, locate a vacant quad slot to accomodate the Q/DH board. If a 16 line unit is being installed, locate two adjacent quad slots. Remove any previously installed bus grant continuity cards from this slot.

The Q/DH is designed to operate in a 4-level interrupt configuration. This means that it will moniter the bus for higher level interrupts. If a higher level interrupt occurs, then the Q/DH will pass the acknowledge signal to the next device on the bus. This allows use of the Q/DH in position-independent arbitration configurations.

If any single-level interrupt devices are used in a position-independent configuration, they must be placed at the end of the bus for arbitration to function properly.

# 3.10 HOW TO INSTALL THE Q/DH INTO YOUR SYSTEM

Prior to installing the Q/DH board, verify that the address and vector switches are set to the desired settings. Insert the board into the selected vacant slot, using the card guides to ensure that it is properly positioned. Insert the board so that it is firmly seated in the slot. If a 16 line unit is being installed, insert the expander board into the second slot and install the interconnect cable.

#### 3.11 INSTALLATION VERIFICATION

# 3.11.1 ZDHM Diagnostics

The Dec ZDHM diagnostic can be used to verify operation of the Q/DH and/or your system. It should be noted, however, that the ZDHM diagnostic will not run as is. The 200 baud level must be disabled by using the patches listed in Table 3-8.

| LOCATION                         | WAS                                                  | IS                           | IS MNEMONIC   |                  |

|----------------------------------|------------------------------------------------------|------------------------------|---------------|------------------|

| 12164<br>12166                   | 62737<br>2100                                        | 4737<br>40000                |               | , PATCH          |

| 12170<br>12472<br>12474          | 1220<br>62737<br>2100                                | 240<br>4737<br>40000         |               | , PATCH          |

| 12476<br>40000<br>40002<br>40004 | 1220 .<br>Don't Care<br>Don't Care<br>Don't Care     | 240<br>62737<br>2100<br>1220 | NOP<br>ADD 2  | 100,STMP7        |

| 40006                            | Don't Care                                           | 22737                        | CMP 20        | 0 BAUD,<br>STMP7 |

| 40010<br>40012<br>40014<br>40016 | Don't Care<br>Don't Care<br>Don't Care<br>Don't Care | 14600<br>1220<br>1771<br>207 | BEQ PA<br>RTS | ТСН              |

Table 3-8: Patches to Dec Diagnostic ZDHM revision DO for the Q/DH

## 3.11.2 Internal Diagnostics

Power can be applied once the Q/DH has been installed into the system. During the power-up sequence, the Q/DH performs an internal diagnostic. This diagnostic verifies a majority of internal operations of the Q/DH. With the maintenance switch set for normal operation, it does not check circuitry that is used to interface to the Q Bus.

The diagnostic mode is switch selectable. Refer to Section 3.7 for proper switch settings.

Proper internal operation of the Q/DH can be verified by monitoring four LEDs near the top of the board. Figure 3-1 shows the location of the LEDs. When power is applied, all four LEDs should light up and after a very short flash, should all turn off. Any LED which remains lit indicates a malfunction and requires investigation. Table 3-7 supplies the definitions of the four LEDs and Chapter 4 provides troubleshooting tips in case an LED remains lit.

PAGE 3-16

If all four LED displays turn off after power has been applied to the system, address the Q/DH through the operator front panel or ODT. Examine the second address assigned to the Q/DH (address 76XXX2, the NRCR register). Immediately following application of power, the Q/DH microcode places the vector settings for the DH and DM devices in this register. Refer to Figure 3-4 for switch verification. If the vector settings are incorrect or the device does not respond, verify the vector and address settings as described in Section 3.5. Repeat the above operation.

If the micro-diagnostics passes, and the address and vector settings have been verified, continue to verify installation of the Q/DH by executing the software diagnostic.

# CHAPTER 4

# What To Do If Q/DH Does Not Work

# 4.1 HOW TO CARE FOR Q/DH

ABLE products are designed to provide years of service with a minimum of care. Here are a few tips to help you avoid problems.

- \* If a printed circuit board is frequently inserted and removed, it tends to build up a gum-like residue on the contacts. Clean this residue off using alcohol or freon. Use of a pencil eraser can remove some of the gold on the contacts, so if you choose to use one, go easy.

- \* Every six months remove each printed circuit board and clean off any accumulated dust. Dust can impede air flow. While the board is out, inspect it for any visual evidence of a potential problem such as damaged components, loose connections, etc.

- \* Schematics for your Q/DH can be ordered from the ABLE factory. Document numbers are listed below.

10176003 Q/DH PC Board

- \* If you wish to maintain a spare parts inventory. Refer to the recommended list in the appendix.

- \* If a problem arises with the operation of your Q/DH, follow the steps outlined in the following sections.

# What To Do If Q/DH Does Not Work

# 4.2 TROUBLESHOOTING TIPS

# 4.2.1 LEDs On

When the ERR LED remains lit, a failure in the micro-diagnostics is indicated. We suggest that you run the power-up sequence a few times to verify consistency of the ERR failure.

If either of the following conditions occur, switch S2 position 2 may be closed and should not be. Check this and all other switch settings.

- \* The ERR LED is off, but other LEDs are lit.

- \* If the ERR LED is lit, LED 2 is lit, LED 3 is off, and LED 1 is in either state.

If the above conditions persist, your Q/DH can be considered faulty. If so, contact the ABLE Product Support Center as outlined in Section 4.3.

An optional switch has been provided which allows progression into the emulation mode if an ERR has occurred in the micro-diagnostic. Section 3.7 provides information on how to set this switch.

In any case, an ERR failure should be reported to the ABLE Product Support Center so that it can be evaluated and resolved.

4.2.2 Verify Configuration And Installation

Experience has shown that the greatest number of problems with Q/DH involve configuration or installation errors. An address, vector, or interrupt level assignment may be inconsistent with system definitions. A correct assignment may be incorrectly specified in the system generation or incorrectly implemented by switch settings or jumper placements.

1. Using Sections 3.5 and 3.6 verify that address and vector assignments and switch settings are correct.

- 2. Using Section 3.8, check that interrupt level jumpers are correctly placed and are making contact.

- 3. Use a voltmeter to verify that the +5V and +12V are within +5% of their nominal value. If not, adjust the associated power supplies using the backplane listed in the Appendix E.

If a fault in a Q/DH board is indicated, call ABLE as described in sections 4.3 and 4.4.

# 4.3 CUSTOMER SERVICE

ABLE Computer's goal is to provide each customer with a product that works well in his system. We design and build our products to provide high reliability and to minimize problems. When a problem does arise, it is our intent to do everything in our power to quickly and efficiently solve it.

4.3.1 Who to Call for Service Within the United States

If your Q/DH does not function properly and you are within the United States, contact our Product Support Center before sending it for repair. Have serial numbers available when calling.

> ABLE Computer 1732 Reynolds Avenue Irvine, California 92714 (714) 979-7030 TWX 910-595-1729

If your product requires repair, we prefer that you return it to the factory. Use the original container or a corregated cardboard carton with at least one inch of cushioning material on all sides. Include a description of the problem and a hard copy of the failure mode or system dump when available. Be sure to include your name, address, and telephone number. Ship it to the above address. 4.3.2 Who to Call for Service Outside the United States

If your Q/DH does not function properly, contact your local distributor or telex ABLE Computer for the name and address of your local distributor:

TWX 910-595-1729

In Europe, telex our London office at:

Telex 848715 ABLE G

Or, our Haar by Munich office at:

Telex 5213883 ABLE D

### CHAPTER 5

#### How To Use Q/DH

### 5.1 TYPICAL APPLICATIONS

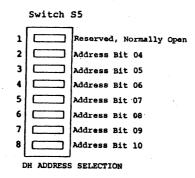

The Q/DH connects a LSI-11 system to eight or sixteen terminals designed to interface with asynchronous communications lines. It provides direct memory access (DMA) output capabilities.

Figure 5-1 illustrates typical interfaces between the Q/DH and local or remote terminals.

The Q/DH is used to interface with local terminal devices or, via modems and dedicated lines, with remote terminal devices. When communicating with remote terminals via datasets that interface over switched networks, modem control is available for all lines.

### 5.2 TERMINAL/COMMUNICATIONS LINK INTERFACE INFORMATION

Table 5-1 lists the pin assignments on connectors J1 on the Q/DH. These connectors provide the interface with the external distribution system for a Q/DH.

PAGE 5-2

Figure 5-1: Q/DH Applications

|           |        | JI   |          |  |

|-----------|--------|------|----------|--|

| DTROO-H   | 1      | 2    | CARROO-H |  |

| DTRO1-H   | 3      | 4    | CARRO1-H |  |

| DTR02-H   | 3<br>5 | 6    | CARRO2-H |  |

| DTR03-H   | 7      | 8    | CARRO3-H |  |

| DTRO4 - H | 9      | 10   | CARRO4-H |  |

| DTR05-H   | 11     | 12   | CARRO5-H |  |

| DTRO6-H   | 13     | 14   | CARRO6-H |  |

| DTRO7 - H | 15     | 16   | CARRO7-H |  |

| MAINT-H   | 17     | 18   | GND      |  |

| TXDOO-H   | 19     | 20   | RINGOO-H |  |

| RXDOO-H   | 21     | 22   | GND      |  |

| TXDO1-H   | 23     | 24   | RINGO1-H |  |

| RXDO1-H   | 25     | 26   | GND      |  |

| TXD02-H   | 27     | 28   | RINGO2-H |  |

| RXD02-H   | 29     | 30   | +5V      |  |

| TXD03-H   | 31     | 32   | RINGO3-H |  |

| RXDO3-H   | 33     | 34 . | +5V      |  |

| TXDO4-H   | 35     | 36   | RINGO4-H |  |

| RXDO4-H   | 37     | 38   | +5       |  |

| TXD05-H   | 39     | 40   | RING05-H |  |

| RXD05-H   | 41     | 42   | -12V     |  |

| TXDO6-H   | 43     | 44   | RINGO6-H |  |

| RXDO6-H   | 45     | 46   | -12V     |  |

| TXD07-H   | 47     | 48   | RINGO7-H |  |

| RXD07-H   | 49     | 50   | -12V     |  |

|           |        |      |          |  |

Table 5-1: Connectors on Q/DH Controller

# 5.3 Q BUS CONNECTOR INFORMATION

Tables 5-2 through 5-5 list Q Bus signals accepted or supplied by the Q/DH via the connectors on the board.

| E 2     | SIDE        | ECTOR A<br>PIN |       | SIDE 1  |

|---------|-------------|----------------|-------|---------|

| 5V      | +5V         | A              |       | BIRQ5-  |

| •       |             | В              |       | BIRQ6-  |

|         | GND         | C              |       | BDAL16  |

| 12V     | +12         | D              | L17-L | BDAL 17 |

| DOUT-L  |             | E              |       |         |

| RPLY-L  |             | F              |       |         |

| DIN-L   |             | Н              |       |         |

| SYNC-L  | BSY         | J              |       | GND     |

| NTBT-L  | BWJ         | K              |       |         |

| IRQ4-L  | BIR         | L              |       |         |

| IAKI-L  | BIA         | М              |       | GND     |

| IAKO-L  | BIA         | N              | R-L   | BDMR-I  |

| BS7-L   | BBS         | Р              |       |         |

| DMGI-L  | BDM         | R              |       |         |

| DMGO-L  | BDM         | S              |       |         |

| INIT-L  | BIN         | T              | . •   | GND     |

| DALOO-L | BDA         | U              |       |         |

| DAL01-L | BDA         | V              |       |         |

| ]       | B<br>B<br>B | S<br>T<br>U    |       | GND     |

Table 5-2: Q/DH Controller Connector A Pin Assignments

| SIDE 1      | CONNECTOR B<br>PIN | SIDE 2      |

|-------------|--------------------|-------------|

| BDCOK-H     | A                  | <b>+</b> 5V |

| BDAL18-L    | B<br>C             | GND         |

| BDAL19-L    | D                  | +12V        |

| BDAL20-L    | Е                  | BDAL02-L    |

| BDAL21-L    | F                  | BDAL03-L    |

|             | H                  | BDAL04-L    |

| GND         | J                  | BDAL05-L    |

|             | K                  | BDAL06-L    |

| <b>a</b> ¥5 | L                  | BDAL07-L    |

| GND         | М                  | BDAL08-L    |

| BSACK-L     | N                  | BDAL09-L    |

| BIRQ7-L     | Р                  | BDAL10-L    |

|             | R                  | BDAL11-L    |

|             | S                  | BDAL12-L    |

| GND         | Т                  | BDAL13-L    |

|             | U                  | BDAL14-L    |

| +5          | V                  | BDAL15-L    |

|             |                    |             |

Table 5-3: Q/DH Controller Connector B Pin Assignments

| SIDE 1 | CONNECTOR C<br>PIN | SIDE 2               |

|--------|--------------------|----------------------|

|        | A                  | + 5V                 |

|        | B<br>C<br>D        | GND<br>+ 1 2 V       |

|        | E<br>F             |                      |

| GND    | H<br>J             |                      |

|        | K<br>L<br>M        | BIAKI-L              |

| GND    | N<br>P             | BIAKO-L<br>BUS-D05-L |

|        | RS                 | BDMGI-L<br>BDMGO-L   |

| GND    | T<br>U<br>V        |                      |

|        | •                  |                      |

Table 5-4: Q/DH Controller Connector C Pin Assignments

| SIDE 1 | CONNECTOR D<br>PIN | SIDE 2 |

|--------|--------------------|--------|

|        | Α                  | +5V    |

|        | В                  |        |

|        | C                  | GND    |

|        | D                  | +12V   |

|        | E                  |        |

|        | F                  |        |

|        | Н                  |        |

| GND    | J                  |        |

|        | K                  |        |

|        | L                  |        |

| GND    | М                  |        |

|        | N                  |        |

|        | P                  |        |

|        | R                  |        |

|        | S                  |        |

| GND    | T t                |        |

|        | Ū                  |        |

| +5V    | v                  |        |

|        | v                  |        |

|        |                    |        |

Table 5-5: Q/DH Controller Connector D Pin Assignments

### CHAPTER 6

#### How To Program Q/DH

### 6.1 DATA HANDLING REGISTERS

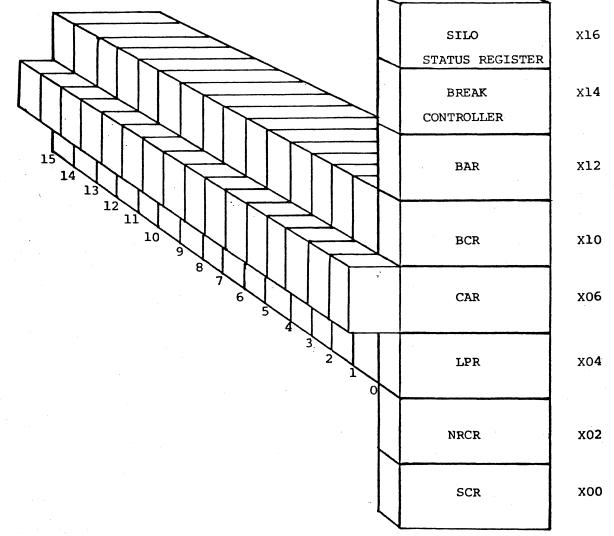

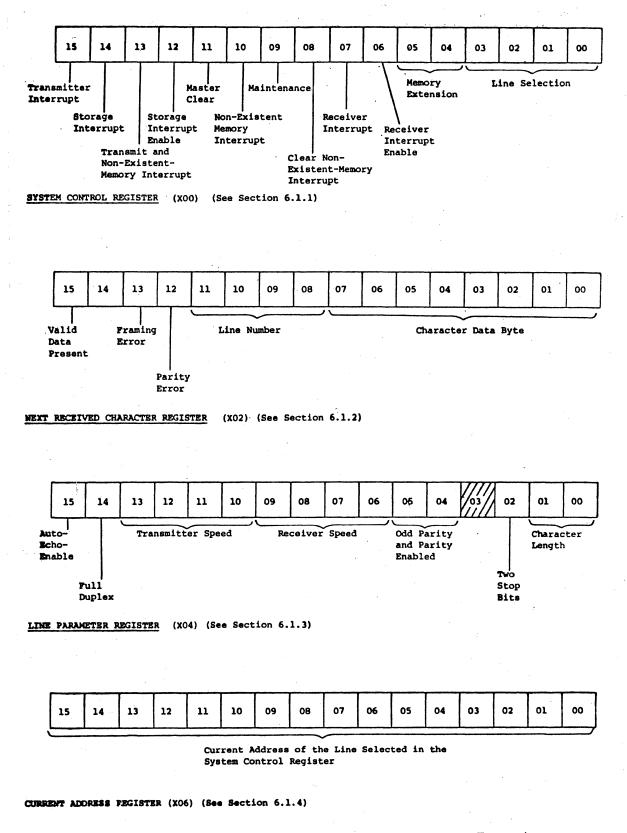

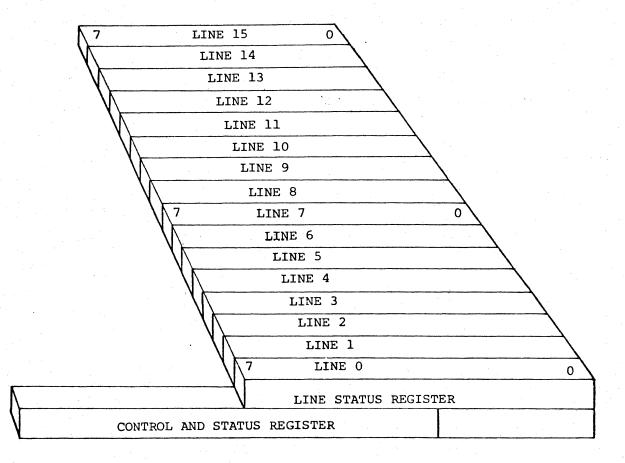

The data handling portion of Q/DH is software compatible with the DEC DH11. It contains eight Q Bus addressable registers. Table 6-1 contains general information about these registers. As illustrated in Figure 6-1, three of these are actually 16-register groups with one register for each line. When one of these groups is addressed, the register within the group is determined by the current line number in the four least significant bit positions of the system control register (SCR). Figure 6-2 illustrates register format. The following paragraphs describe the function of each register.

6.1.1 System Control Register

- Bit Description

- 15 <u>Transmitter Interrupt</u>. This read/write bit is set when the final character in a message buffer is loaded into a UART transmitter holding register. It causes an interrupt if bit 13 is set.

- 14 <u>Storage Interrupt.</u> This bit is set when a character transfer from a receiver holding register to the silo is inhibited because the silo is full. It causes an interrupt if bit 12 is set. This bit is read only in the normal mode and read/write in the maintenance mode. When not in the maintenance mode, the silo has a 255 character capacity.

| REGISTER                            | ADDRESS | ACCESS             | WORD/BYTE<br>ADDRESSABLE |

|-------------------------------------|---------|--------------------|--------------------------|

| System Control<br>Register          | X00     | Mixed<br>See 6.1.1 | Word/Byte                |

| Next Received<br>Character Register | X02     | Read Only          | Word Only                |

| Line Parameter<br>Register (Group)  | X04     | Read/Write         | Word Only                |

| Current Address<br>Register         | X06     | Read/Write         | Word Only                |

| Byte Count<br>Register (Group)      | X10     | Read/Write         | Word Only                |

| Buffer Active<br>Register           | X12     | Read/Write         | Word Only                |

| Break Control<br>Register           | X 1 4   | Read/Write         | Word Only                |

| Silo Status<br>Register             | X16     | Mixed<br>See 6.1.8 | Word/Byte                |

Table 6-1: Data Handling Register List

Figure 6-1: Data Handling Registers

PAGE 6-3

Figure 6-2: Data Handling Register Formats

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |   |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|

|    |    |    | L  |    |    |    |    |    |    |    |    |    |    |    |    | ļ |

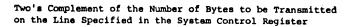

BYTE COUNT REGISTER (X10) (See Section 6.1.5)

Transmit Enable, Line 15 - 00

BUFFER ACTIVE REGISTER (X12) (See Section 6.1.6)

Break Bit, Line 15 - 00

BREAK CONTROL REGISTER (X14) (See Section 6.1.7)

Figure 6-2: Data Handling Register Formats (Con't.)

13

12

11

09

80

07

| Bit Description | В | i | t |  | De | sc | er | i | р | t | i | 0 | 'n |

|-----------------|---|---|---|--|----|----|----|---|---|---|---|---|----|

|-----------------|---|---|---|--|----|----|----|---|---|---|---|---|----|

Transmit and Non-Existent-Memory Interrupt Enable. When set, this read/write bit enables an interrupt in response to the setting of bits 10 or 15.

Storage Interrupt Enable. When set, this read/write bit enables an interrupt in response to the setting of bit 14.

- Master Clear. When set, write only bit places the data handling portion of the Q/DH in the initialized status in which the silo, the UART's, and most register bits are cleared.

- 10 <u>Non-Existent-Memory</u> <u>Interrupt.</u> This bit is set if no RPLY response is received within 20 microseconds of the assertion of DIN by the Q/DH during a DMR transaction. The lack of response indicates that the addressed memory location does not exist. Setting this bit causes an interrupt if bit 13 is set. This bit is read only in the normal mode and read/write in the maintenance mode.

- Maintenance. When set, this read/write bit places the Q/DH in the maintenance mode.

<u>Clear Non-Existent-Memory Interrupt.</u> When set, this bit clears bit 10 and itself.

Receiver Interrupt. This bit is set when the number of characters stored in the silo exceeds the alarm level specified by the low byte of the silo status register. It generates an interrupt if bit 06 is set. This bit is read only in the normal mode and is read/write in the maintenance mode. If there are fewer than sixteen characters in the silo and S3-3 is closed, there will be a delay of about 20ms before this bit is set. This reduces interrupt overhead when a line is used as a link to another computer.

06

<u>Receiver</u> <u>Interrupt</u> <u>Enable</u>. When set, this read/write bit enables an interrupt in response to the setting of bit 07.

## Bit Description

- 05,04 <u>Memory Extension</u>. When the program writes the current address register for the line selected by bits 03 through 00, read/write bits 05 and 04 are written into bits 17 and 16 of that current address register. When the system control register is read, the bit 05 and 04 values are those most recently written into these bit positions. Notice that these are not necessarily the current values of bits 17 and 16 of the Current Address Register for the currently selected line.

- 03 00 Line Selection. These read/write bits specify the line (horizontal) address of the register to be written or read when the line parameter, current address, or byte count register is addressed.

- 6.1.2 Next Received Character Register (XO2)

- Bit Description

- 15 <u>Valid Data Present</u>. This bit is set when the remaining bit positions of the register contain valid information and is reset when the register is empty.

- 14 <u>Data Overrun</u>. This bit is set when at least one preceding character of the same message has been overwritten and lost in the UART holding register.

- 13 Framing Error. This bit is set when the current character is not framed by the programmed number of stop bits. This is usually interpreted as the reception of a break.

- 12 <u>Parity Error</u>. This bit is set when the current character exhibits incorrect parity as received from the line.

- 11 08 Line Number. These bits contain the number of the line from which the character was received.

- 07 00 Character Data Byte. This byte contains the data bits of a character from the line whose number appears in bits 11 through 08. When the character has less than eight data bits, these bits are right-justified and unused bits of the byte are zeros.

PAGE 6-8

### 6.1.3 Line Parameter Register (XO4)

Prior to transmitting or receiving messasges on a line, the program must define certain parameters for the line by writing the line parameter register. In order to write into the line parameter register for a line, that line number must first be written into the system control register. The line parameter register is a read/write operation register, but when read it reflects the value last written, and not the value for the currently selected line.

- Bit Description

- 15

14

- <u>Auto-Echo-Enable.</u> When this bit is set, characters received on the line are automatically transmitted back (echoed) on the line by Q/DH.

- Half/Full Duplex. In the full duplex mode (bit 14=0), transmission and reception can occur simultaneously. In half duplex mode (bit 14=1), the receiver is disabled when characters are being transmitted.

- 13 10 <u>Transmitter Speed</u>. These bits define the transmitter baud rate in the table following.

| 13 | 12 | 11 | 10 | Speed<br>(Baud) | 13 | 12 | 11 | 10 | Speed<br>(Baud) |

|----|----|----|----|-----------------|----|----|----|----|-----------------|

| 0  | 0  | 0  | 0  | Zero            | 1  | 0  | 0  | 0  | 600             |

| 0  | 0  | 0  | 1  | 50              | 1  | 0  | 0  | 1  | 1200            |

| 0  | 0  | 1  | 0  | 75              | 1  | 0  | 1  | 0  | 1800            |

| 0  | 0  | 1  | 1  | 110             | 1  | 0  | 1. | 1  | 2400            |

| 0  | 1  | 0  | 0  | 134.5           | 1  | 1  | 0  | 0  | 4800            |

| 0  | 1  | 0  | 1  | 150             | 1  | 1  | 0  | 1  | 9600            |

| 0  | 1  | 1  | 0  | Invalid         | 1  | 1  | 1  | 0  | 19200           |

| 0  | 1  | 1  | 1  | 300             | 1  | 1  | 1  | 1  | Invalid         |

Table 6-2: Transmitter Baud Rate

PAGE 6-9

#### NOTE

The following restrictions are associated with line speed selection:

- Speed codes 6 (200 baud) and 15 (External B) are not valid.

- 2. One circuit has been provided for support of split speed operation. Differing receive and transmit speeds can be selected for a given line, however, the receive speed selected may not differ from some other split receive speed already in effect.

- 09 06 Receiver Speed. These bits define the receiver bit rate in the same manner and with the same restrictions that bits 13 - 10 define the transmitter baud rate.

- Bit Description

- 05,04

Odd Parity and Parity Enabled. The combined states of these bits determine the parity generated by the UART transmitter and the parity required by the UART receiver for the line as follows:

| 05 | 04 | Parity |

|----|----|--------|

| 0  | 0  | None   |

| 0  | 1  | Even   |

| 1  | 0  | None   |

| 1  | 1  | Odd    |

|  | 0 | 3 | Not | Used. |

|--|---|---|-----|-------|

|--|---|---|-----|-------|

Two Stop Bits. When this bit is set, 1.5 stop bits are appended to transmitted characters having 5 data bits; and 2 stop bits are appended to transmitted characters having from 6 through 8 data bits. When this bit is reset, one stop bit is appended to all transmitted characters regardless of length. Recieved characters are always checked for one stop bit.

01,00 <u>Character Length</u>. These two bits specify the number of data bits in received and transmitted characters as follows:

| 01 | 00 | Data<br>Bits |

|----|----|--------------|

| 0  | 0  | 5            |

| 0  | 1  | 6            |

| 1  | 0  | 7            |

| 1  | 1  | 8            |

#### 6.1.4 Current Address Register (X06)

Prior to transmitting a message over a line, the program must write the starting address of the data buffer containing the message into the current address register for that line. This involves first writing the line number and the address extension bits into the system control register and then transferring the remainder of the starting address directly to the current address register. During this second transfer, Q Bus bits 00 through 15 are written into bit positions 00 through 15 of the current address register and the address extension bits from bit positions 04 and 05 of the system control register are written into bit positions 16 and 17 of the current address register. To read the current address for a line, the program must write the line number into the system control register. It can then read bits 00 through 15 of the current address by reading the current address register and bits 16 through 17 by reading the silo status register which contains these bits in bit positions 06 and 07.

The Q/DH has an extended mode to allow 22 bit DMA operations. In this mode, the lower 16 bits are loaded as above. Then bit 14 of the silo status register is written with a one, and the upper 6 bits of the 22 bit address are written into the lower 6 bits of the current address register. At that time, bit 14 of the SSR is automatically cleared.

#### 6.1.5 Byte Count Register (X10)

Prior to transmitting a message over a line, the program must also write the 2's complement of the number of characters (bytes) in the message into the byte count register. As in the case of the line parameter and current address register, the line number must first be written into the system control register in order to address the byte count register for the line. The byte count register can then be either written or read by the program.

#### 6.1.6 Buffer Active Register (X12)

This register contains one bit for each line; bit n is for line n. The program sets bit n to start transmission of a message over line n after the message has been written in a data buffer in LSI-11 memory and the starting address and length of the data buffer have been transferred to the current address register and byte count register for the line. The Q/DH subsequently resets the bit for the line at the time that the last character of the message is loaded into the UART holding register. Because the Q/DH resets the bits in this register, the program must use BIS instructions to set these bits.

#### 6.1.7 Break Control Register (X14)

This register contains one bit for each line; bit n is for line n. The program sets the bit for a line to start the transmission of a break on that line and resets the bit to terminate the transmission of the break. (Refer to paragraph 6.4 for break control timing information.)

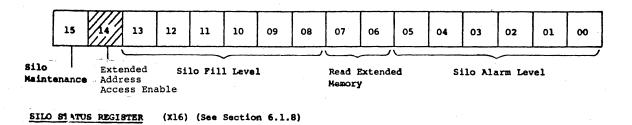

#### 6.1.8 Silo Status Register (X16)

Bit Description

- 15 <u>Silo Maintenance</u>. When set, this read/write bit causes a fixed binary pattern to be sent to the silo for checking. To send more characters, this bit must be cleared and then set again.

- 14 Extended Address Access Enable. When this read/write bit is set, the upper 6 bits of the full 22 bit DMA address may be read from or written to the low 6 bits of the CAR. This bit is cleared when the CAR is accessed

- 13 08 Silo Fill Level. These read-only bits indicate the number of characters currently held in the silo. 000000 can indicate either an empty silo or a silo with more than 63 characters. For an empty silo, the valid data present bit (15) of the next received character register is reset while for a silo with more than 63 characters, it is set. Also, if an attempt has been made to load another character into a full silo, then the storage overflow bit (14) of the system control register is set.

- 07,06 Read Extended Memory. These read-only bits are A17 and A16 of the current address register for the line whose number is held in the line selection field (bits 03 through 00) of the system control register.

- 05 00 Silo Alarm Level. When the silo fill level exceeds the value written into this read/write field by the program, receiver interrupt bit 07 of the system control register is set. If receiver interrupt enable bit 06 of the system control register is set, this causes an interrupt. If there are fewer than sixteen characters in the silo and S3-3 is closed there will be a delay of 20ms before this bit is set. This reduces interrupt overhead when a line is used as a link to another computer.

### 6.2 MODEM REGISTERS

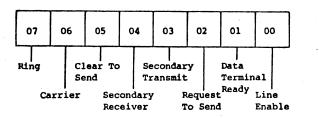

The DM portion implements a software compatible subset of the DEC DM11-BB. It contains two Q Bus addressable registers, the control and status register and the line status register. As illustrated in Figure 6-3, the byte-wide line status register is actually a register group

#### How To Program Q/DH

that includes one register for each line. When the line status register group is addressed, the particular register is read or written as determined by the line number held in the control and status register. The following paragraphs describe the two registers. Figure 6-4 illustrates register formats.

The only actual signals are Ring, Carrier, and Data Terminal Ready. All others are simulated for software compatibility.

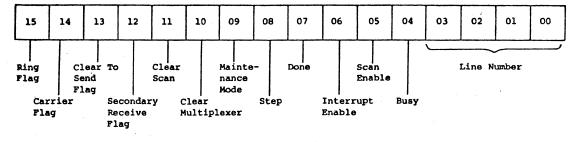

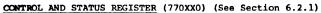

#### 6.2.1 Control and Status Register

#### Bit Description

<u>Ring Flag.</u> This read-only bit and DONE (bit 07) are set when a transition from OFF to ON is detected for the RING signal from the line specified by bits 03 through 00. Setting CLEAR SCAN (bit 01) resets the stored value of RING so that an existing ON condition appears as a transition and sets this bit and DONE.

14

15

Carrier Flag. This read-only bit and DONE (bit 07) are set when any transition of the CARRIER signal from the line specified by bits 03 through 00 is detected. Setting CLEAR SCAN (bit 11) resets the stored value of CARRIER so that an existing ON condition appears as a transition and sets this bit and DONE.

13

<u>Clear to Send Flag.</u> This read-only bit and DONE (bit 07) are set when any transition of the CLEAR TO SEND signal from the line specified by bits 03 through 00 is detected. Setting CLEAR SCAN (bit 11) resets the stored value of CLEAR TO SEND so that an existing ON conditon appears as a transition and sets this bit and DONE.

NOTE

Figure 6-3: Modem Registers

LINE STATUS REGISTER (770XX2) (See Section 6.2.2)

Figure 6-4: Modem Register Formats

#### Description

Secondary Receive Flag. This read-only bit and DONE (bit 07) are set when any transition of the SECONDARY RECEIVE signal from the line specified by bits 03 through 00 is detected. Setting CLEAR SCAN (bit 11) resets the stored value of SECONDARY RECEIVE so that an existing ON condition appears as a transition and sets this bit and the DONE bit.

11

Bit

12

- <u>Clear Scan.</u> Writing a ONE into this write-<u>ONE-only bit clears bits 09, 07, 06, 05 and 03</u> through 00 and initiates a sequence which clears the scan memory. With the scan memory cleared, any ON condition of a RING, CARRIER, SEND, or SECONDARY RECEIVE signal is detected as a change of state during subsequent scanning and causes the associated change flag (bits 15 through 12) to set.

- <u>Clear Multiplexer.</u> Writing a ONE into this write-ONE-only bit clears bits 03 through 00 (SECONDARY TRANSMIT, REQUEST TO SEND, DATA TERMINAL READY, LINE ENABLE) of all 16 line status registers.

- Maintenance Mode. Setting this read/write bit forces the RING, CARRIER, CLEAR TO SEND, and SECONDARY RECEIVE inputs to the line scanner to the ON condition for test purposes. If this is preceded by the writing of a ONE into CLEAR SCAN (bit 11) then an interrupt (if enabled) should be generated for every line that is scanned.

Step. Each time that a ONE is written into this write-ONE-only bit, a STEP sequence is initiated. During this sequence, the line number held in bits O3 through OO is incremented, signals from the newly addressed line are evaluated for transitions, and change flags (bit 15 through 12) and the DONE flag (bit 07) are set if any transitions are detected. This bit can be used rather than SCAN ENABLE (bit 05) to provide a scan rate controlled by the program. Note, however, that this scan rate should be high enough so that CARRIER signals will not switch ON and OFF during the interval between successive scans of a line. Note also, that DONE does not inhibit STEP.

09

80

10

| Bit | Description |      |         |  |

|-----|-------------|------|---------|--|

| 07  | Done.       | This | read/wr |  |

Done. This read/write bit is set when bit 15, 14, 13, or 12 sets. With DONE set, the line scanner is disabled so that bits 03 through 00 contain the number of the line associated with the condition which causes DONE to set. If INTERRUPT ENABLE bit 06 is also set, an interrupt routine normally resets DONE so as to release the line scanner. This bit is also reset by INITIALIZE and by CLEAR SCAN (bit 11).

06

05

Interrupt Enable. When this read/write bit is set, the DM interrupt function is enabled. The bit is cleared by INITIALIZE and by CLEAR SCAN (bit 11).

Scan Enable. When this read/write bit is set the DM is placed in the automatic scanning mode. In this mode, the scanner increments the line number held in bits 03 through 00 and checks for transitions of the signals from the newly addressed line until a transition is found. At this time the appropriate transition flag (bits 15 through 12) and DONE (bit 07) are set. Scanning is then inhibited until the program resets the DONE bit.

Busy. This read-only bit is set when lines are being scanned. The program should change line numbers (bits 03 through 00) only when BUSY is 0. 03 - 00 Line Number. These read/write bits, held in a counter, point to one of the 16 line-status registers and select inputs from one of the 16 lines for transition detection. The line number is incremented at the start of each scan cycle and is reset to 0000 by INITIALIZE or by CLEAR SCAN (bit 11). Notice, that since the incrementing of the count occurs at the start of each scan cycle, the first line tested after a reset is 0001 rather than 0000.

#### 6.2.2 Line Status Register

- Bit Description

- 07 <u>Ring.</u> This read-only bit indicates the status of the modem RING signal.

- 06 <u>Carrier</u>. This read-only bit indicates the status of the modem CARRIER signal.

- Clear to Send. This read-only bit indicates the

04

05

04

03

status of the modem CARRIER signal. This is done for software compatibility.

Secondary Receive. This bit is a read-only copy of the SECONDARY TRANSMIT bit (03).

Secondary Transmit. This bit is copied into SECONDARY RECEIVE (04) for diagnostic compatibility. This bit is reset by INITIALIZE or by CLEAR MUX (bit 10) of the control and status register.

- 02 Request to Send. This bit is not used. The bit is cleared by INITIALIZE and CLEAR MUX. It is read/write.

- 01 <u>Data Terminal Ready</u>. This bit allows the modem to maintain the data mode. It is cleared by INITIALIZE and CLEAR MUX. This bit is read/write.

- 00 Line Enable. This bit enables the state of RING, CARRIER, CLEAR TO SEND, and SEC RX to be sampled by the program and tested for transitions. It is cleared by INITIALIZE and CLEAR MUX. This bit is read/write.